8-16

DSP56367

MOTOROLA

Host Interface (HDI08)

HDI08 – DSP-Side Programmer’s Model

8.5.6.14

HPCR Host Chip Select Polarity (HCSP) Bit 13

If the HCSP bit is cleared, the chip select (HCS) signal is configured as an active low input

and the HDI08 is selected when the HCS signal is low. If HCSP is set, HCS is configured as

an active high input and the HDI08 is selected when the HCS signal is high. This bit is ignored

in the multiplexed mode.

8.5.6.15

HPCR Host Request Polarity (HRP) Bit 14

The HRP bit controls the polarity of the host request signals. In the single host request mode

(HDRQ=0 in the ICR), if HRP is cleared and host requests are enabled (HREN=1 and HEN=1

in the HPCR), the HOREQ signal is an active low output. If HRP is set and host requests are

enabled, the HOREQ signal is an active high output.

In the double host request mode (HDRQ=1 in the ICR), if HRP is cleared and host requests

are enabled (HREN=1 and HEN=1 in the HPCR), the HTRQ and HRRQ signals are active

low outputs. If HRP is set and host requests are enabled, the HTRQ and HRRQ signals are

active high outputs.

8.5.6.16

HPCR Host Acknowledge Polarity (HAP) Bit 15

If the HAP bit is cleared, the host acknowledge (HACK) signal is configured as an active low

input, and the HDI08 drives the contents of the HIVR register onto the host bus when the

HACK signal is low. If HAP is set, HACK is configured as an active high input, and the

HDI08 outputs the contents of the HIVR register when the HACK signal is high.

8.5.7

DATA DIRECTION REGISTER (HDDR)

The HDDR controls the direction of the data flow for each of the HDI08 pins configured as

GPIO. Even when the HDI08 is used as the host interface, some of its unused signals may be

configured as GPIO pins. For information on the HDI08 GPIO configuration options, see

Section 8.6.8. If bit DRxx is set, the corresponding HDI08 pin is configured as an output

signal. If bit DRxx is cleared, the corresponding HDI08 pin is configured as an input signal.

See Table 8-6.

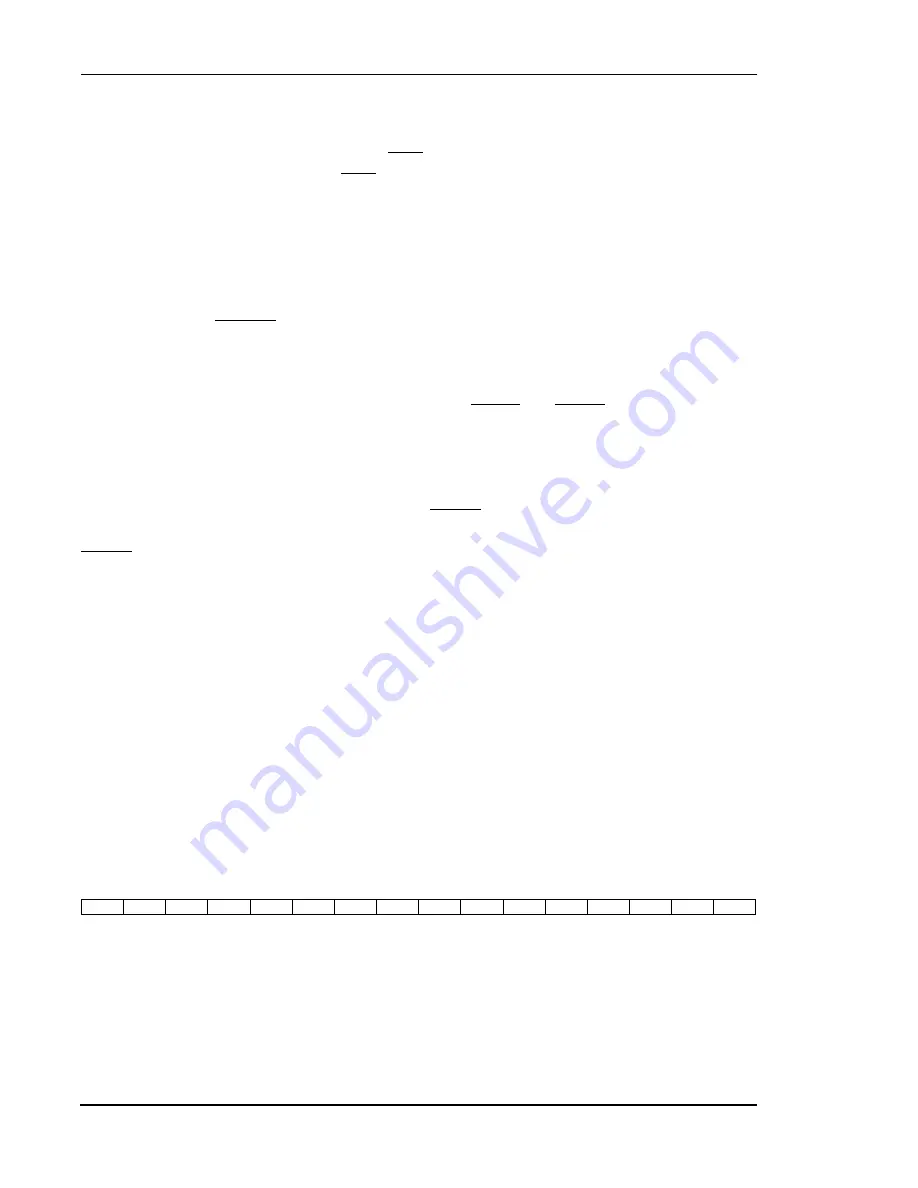

Figure 8-9 Host Data Direction Register (HDDR) (X:$FFFFC8)

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

DR15

DR14

DR13

DR12

DR11

DR10

DR9

DR8

DR7

DR6

DR5

DR4

DR3

DR2

DR1

DR0

Summary of Contents for DSP56367

Page 16: ...xvi MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 22: ...xxii MOTOROLA List of Figures Figure Number Title Page Number ...

Page 26: ...xxvi MOTOROLA List of Tables Table Number Title Page Number ...

Page 148: ...4 6 DSP56367 MOTOROLA Design Considerations PLL Performance Issues ...

Page 248: ...9 30 DSP56367 MOTOROLA Serial Host Interface SHI Programming Considerations ...

Page 306: ...10 58 DSP56367 MOTOROLA Enhanced Serial Audio Interface ESAI ESAI Initialization Examples ...

Page 389: ...Bootstrap ROM Contents MOTOROLA DSP56367 A 15 end ...

Page 390: ...A 16 DSP56367 MOTOROLA Bootstrap ROM Contents ...

Page 432: ...C 8 DSP56367 MOTOROLA JTAG BSDL ...

Page 484: ...D 52 DSP56367 MOTOROLA Programmer s Reference ...

Page 490: ...E 6 DSP56367 MOTOROLA Power Consumption Benchmark ...

Page 516: ...F 26 DSP56367 MOTOROLA IBIS Model ...

Page 522: ...Index 6 MOTOROLA Index ...

Page 523: ......