8-24

DSP56367

MOTOROLA

Host Interface (HDI08)

HDI08 – External Host Programmer’s Model

The size of the DMA word to be transferred is determined by the DMA control bits, HM0 and

HM1. The HDI08 host side data register selected during a DMA transfer is determined by a

2-bit address counter, which is preloaded with the value in HM1 and HM0. The address

counter substitutes for the HA1 and HA0 host address signals of the HDI08 during a DMA

transfer. The host address signal HA2 is forced to one during each DMA transfer. The address

counter can be initialized with the INIT bit feature. After each DMA transfer on the host data

bus, the address counter is incremented to the next data register. When the address counter

reaches the highest register (RXL or TXL), the address counter is not incremented but is

loaded with the value in HM1 and HM0. This allows 8-, 16- or 24-bit data to be transferred in

a circular fashion and eliminates the need for the DMA controller to supply the HA2, HA1,

and HA0 address signals. For 16- or 24-bit data transfers, the DSP CPU interrupt rate is

reduced by a factor of 2 or 3, respectively, from the host request rate – i.e., for every two or

three host processor data transfers of one byte each, there is only one 24-bit DSP CPU

interrupt.

If either HDM1 or HDM0 in the HCR register are set, bits 6 and 5 become read-only bits that

reflect the value of HDM[1:0].

8.6.1.8

ICR Initialize Bit (INIT) Bit 7

The INIT bit is used by the host processor to force initialization of the HDI08 hardware.

During initialization, the HDI08 transmit and receive control bits are configured.

Using the INIT bit to initialize the HDI08 hardware may or may not be necessary, depending

on the software design of the interface.

The type of initialization done when the INIT bit is set depends on the state of TREQ and

RREQ in the HDI08. The INIT command, which is local to the HDI08, is designed to

conveniently configure the HDI08 into the desired data transfer mode. The effect of the INIT

command is described in Table 8-13. When the host sets the INIT bit, the HDI08 hardware

executes the INIT command. The interface hardware clears the INIT bit after the command

has been executed.

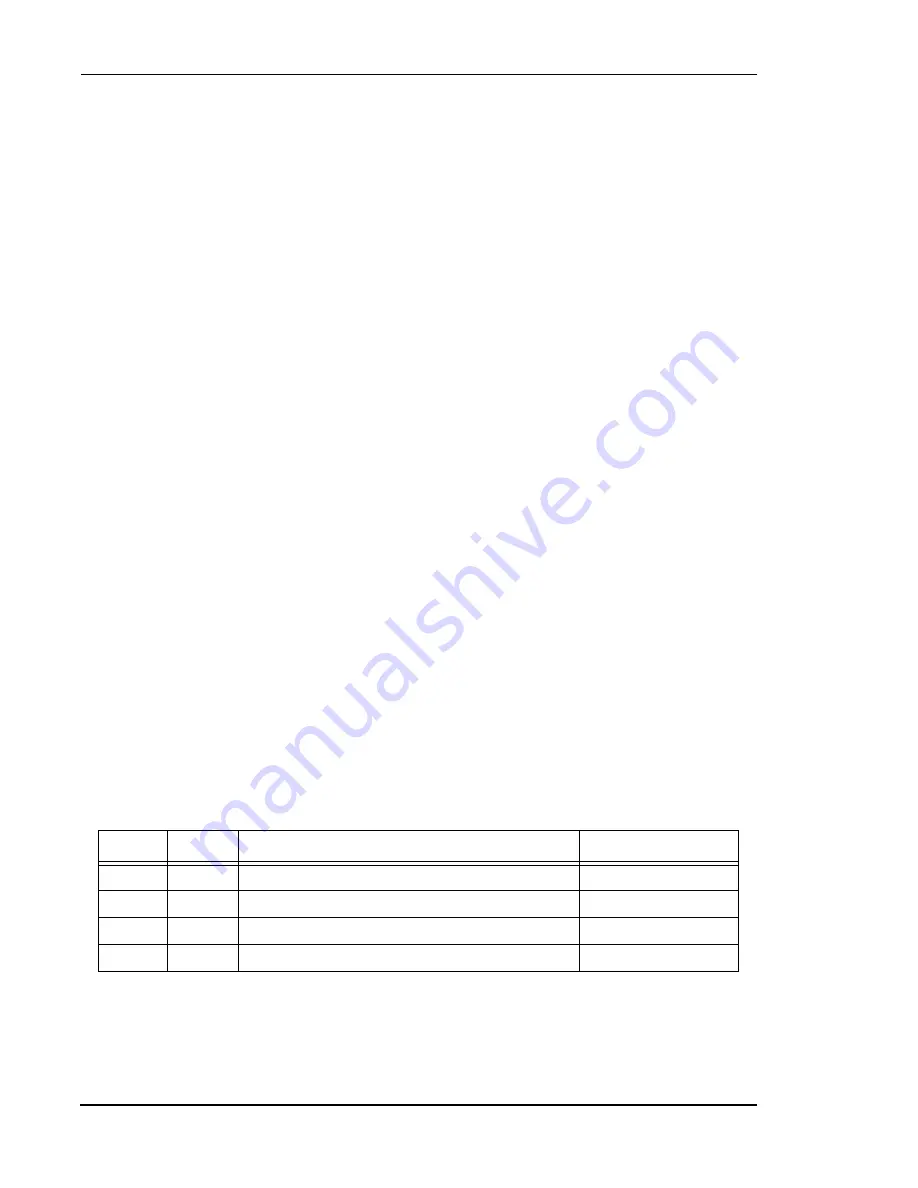

Table 8-13 INIT Command Effect

TREQ

RREQ

After INIT Execution

Transfer Direction Initialized

0

0

INIT=0

None

0

1

INIT=0; RXDF=0; HTDE=1

DSP to Host

1

0

INIT=0; TXDE=1; HRDF=0

Host to DSP

1

1

INIT=0; RXDF=0; HTDE=1; TXDE=1; HRDF=0

Host to/from DSP

Summary of Contents for DSP56367

Page 16: ...xvi MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 22: ...xxii MOTOROLA List of Figures Figure Number Title Page Number ...

Page 26: ...xxvi MOTOROLA List of Tables Table Number Title Page Number ...

Page 148: ...4 6 DSP56367 MOTOROLA Design Considerations PLL Performance Issues ...

Page 248: ...9 30 DSP56367 MOTOROLA Serial Host Interface SHI Programming Considerations ...

Page 306: ...10 58 DSP56367 MOTOROLA Enhanced Serial Audio Interface ESAI ESAI Initialization Examples ...

Page 389: ...Bootstrap ROM Contents MOTOROLA DSP56367 A 15 end ...

Page 390: ...A 16 DSP56367 MOTOROLA Bootstrap ROM Contents ...

Page 432: ...C 8 DSP56367 MOTOROLA JTAG BSDL ...

Page 484: ...D 52 DSP56367 MOTOROLA Programmer s Reference ...

Page 490: ...E 6 DSP56367 MOTOROLA Power Consumption Benchmark ...

Page 516: ...F 26 DSP56367 MOTOROLA IBIS Model ...

Page 522: ...Index 6 MOTOROLA Index ...

Page 523: ......