Serial Host Interface

Serial Host Interface Programming Model

MOTOROLA

DSP56367

9-13

9.5.6

SHI CONTROL/STATUS REGISTER (HCSR)—DSP SIDE

The HCSR is a 24-bit register that controls the SHI operation and reflects its status. The

control bits are read/write. The status bits are read-only. The bits are described in the

following paragraphs. When in the stop state or during individual reset, the HCSR status bits

are reset to their hardware-reset state, while the control bits are not affected.

9.5.6.1

HCSR Host Enable (HEN)—Bit 0

The read/write control bit HEN, when set, enables the SHI. When HEN is cleared, the SHI is

disabled (that is, it is in the individual reset state, see below). The HCKR and the HCSR

control bits are not affected when HEN is cleared. When operating in master mode, HEN

should be cleared only when the SHI is idle (HBUSY = 0). HEN is cleared during hardware

reset and software reset.

9.5.6.1.1

SHI Individual Reset

While the SHI is in the individual reset state, SHI input pins are inhibited, output and

bidirectional pins are disabled (high impedance), the HCSR status bits and the

transmit/receive paths are reset to the same state produced by hardware reset or software reset.

The individual reset state is entered following a one-instruction-cycle delay after clearing

HEN.

9.5.6.2

HCSR I

2

C/SPI Selection (HI

2

C)—Bit 1

The read/write control bit HI

2

C selects whether the SHI operates in the I

2

C or SPI modes.

When HI

2

C is cleared, the SHI operates in the SPI mode. When HI

2

C is set, the SHI operates

in the I

2

C mode. HI

2

C affects the functionality of the SHI pins as described in Section 2,

Signal/Connection Descriptions. It is recommended that an SHI individual reset be generated

(HEN cleared) before changing HI

2

C. HI

2

C is cleared during hardware reset and software

reset.

9.5.6.3

HCSR Serial Host Interface Mode (HM[1:0])—Bits 3–2

The read/write control bits HM[1:0] select the size of the data words to be transferred, as

shown in Table 9-4. HM[1:0] should be modified only when the SHI is idle (HBUSY = 0).

HM[1:0] are cleared during hardware reset and software reset.

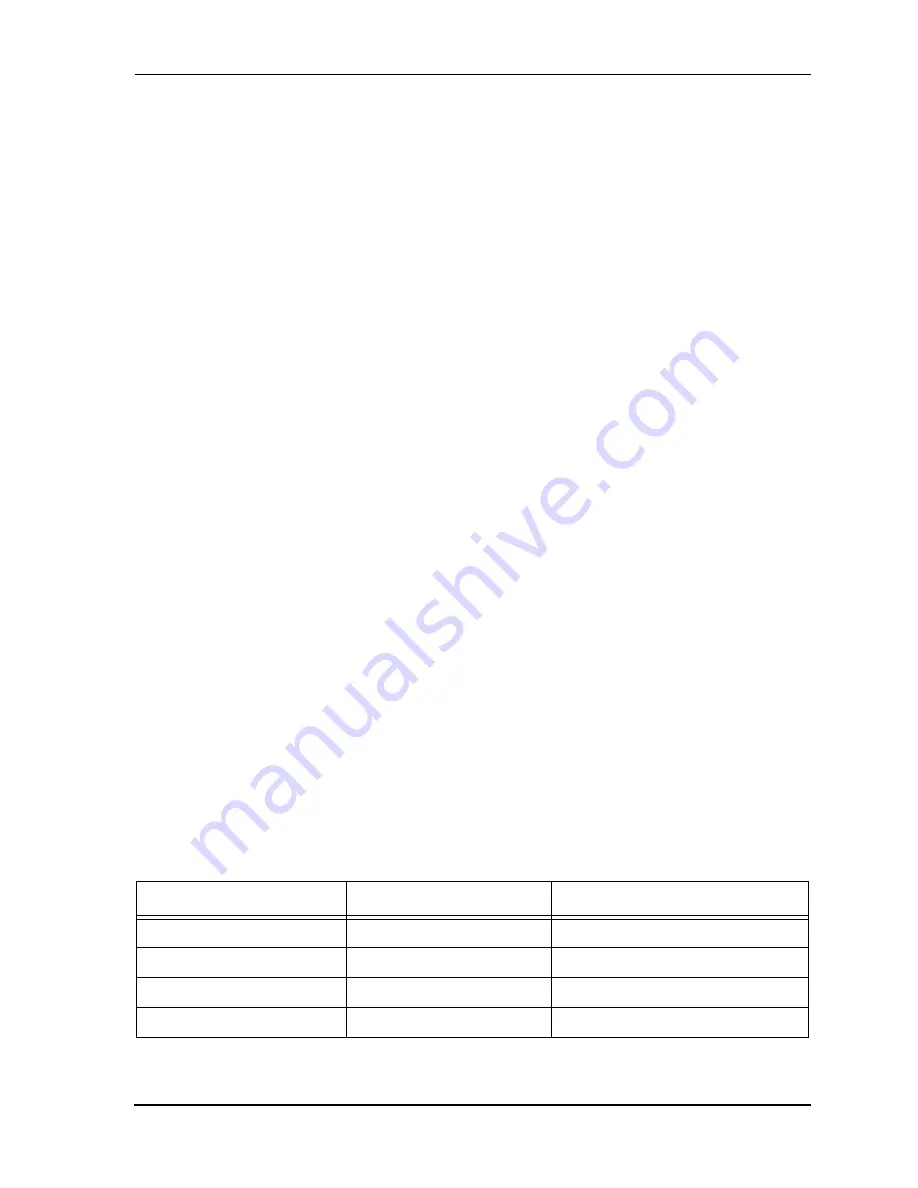

Table 9-4 SHI Data Size

HM1

HMO

Description

0

0

8-bit data

0

1

16-bit data

1

0

24-bit data

1

1

Reserved

Summary of Contents for DSP56367

Page 16: ...xvi MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 22: ...xxii MOTOROLA List of Figures Figure Number Title Page Number ...

Page 26: ...xxvi MOTOROLA List of Tables Table Number Title Page Number ...

Page 148: ...4 6 DSP56367 MOTOROLA Design Considerations PLL Performance Issues ...

Page 248: ...9 30 DSP56367 MOTOROLA Serial Host Interface SHI Programming Considerations ...

Page 306: ...10 58 DSP56367 MOTOROLA Enhanced Serial Audio Interface ESAI ESAI Initialization Examples ...

Page 389: ...Bootstrap ROM Contents MOTOROLA DSP56367 A 15 end ...

Page 390: ...A 16 DSP56367 MOTOROLA Bootstrap ROM Contents ...

Page 432: ...C 8 DSP56367 MOTOROLA JTAG BSDL ...

Page 484: ...D 52 DSP56367 MOTOROLA Programmer s Reference ...

Page 490: ...E 6 DSP56367 MOTOROLA Power Consumption Benchmark ...

Page 516: ...F 26 DSP56367 MOTOROLA IBIS Model ...

Page 522: ...Index 6 MOTOROLA Index ...

Page 523: ......