Serial Host Interface

Serial Host Interface Programming Model

MOTOROLA

DSP56367

9-17

Note:

Clearing HRIE[1:0] masks a pending receive interrupt only after a one instruction

cycle delay. If HRIE[1:0] are cleared in a long interrupt service routine, it is

recommended that at least one other instruction separate the instruction that clears

HRIE[1:0] and the RTI instruction at the end of the interrupt service routine.

9.5.6.12

HCSR Host Transmit Underrun Error (HTUE)—Bit 14

The read-only status bit HTUE indicates whether a transmit-underrun error occurred.

Transmit-underrun errors can occur only when operating in the SPI slave mode or the I

2

C

slave mode when HCKFR is cleared. In a master mode, transmission takes place on demand

and no underrun can occur. HTUE is set when both the shift register and the HTX register are

empty and the external master begins reading the next word:

•

When operating in the I

2

C mode, HTUE is set in the falling edge of the ACK bit. In

this case, the SHI retransmits the previously transmitted word.

•

When operating in the SPI mode, HTUE is set at the first clock edge if CPHA = 1; it is

set at the assertion of SS if CPHA = 0.

If a transmit interrupt occurs with HTUE set, the transmit-underrun interrupt vector is

generated. If a transmit interrupt occurs with HTUE cleared, the regular transmit-data

interrupt vector is generated. HTUE is cleared by reading the HCSR and then writing to the

HTX register. HTUE is cleared by hardware reset, software reset, SHI individual reset, and

during the stop state.

9.5.6.13

HCSR Host Transmit Data Empty (HTDE)—Bit 15

The read-only status bit HTDE indicates whether the HTX register is empty and can be

written by the DSP. HTDE is set when the data word is transferred from HTX to the shift

register, except in SPI master mode when CPHA = 0 (see HCKR). When in the SPI master

mode with CPHA = 0, HTDE is set after the end of the data word transmission. HTDE is

cleared when the DSP writes the HTX either with write instructions or DMA transfers. HTDE

is set by hardware reset, software reset, SHI individual reset, and during the stop state.

9.5.6.14

HCSR Reserved Bits—Bits 23, 18 and 16

These bits are reserved. They read as zero and should be written with zero for future

compatibility.

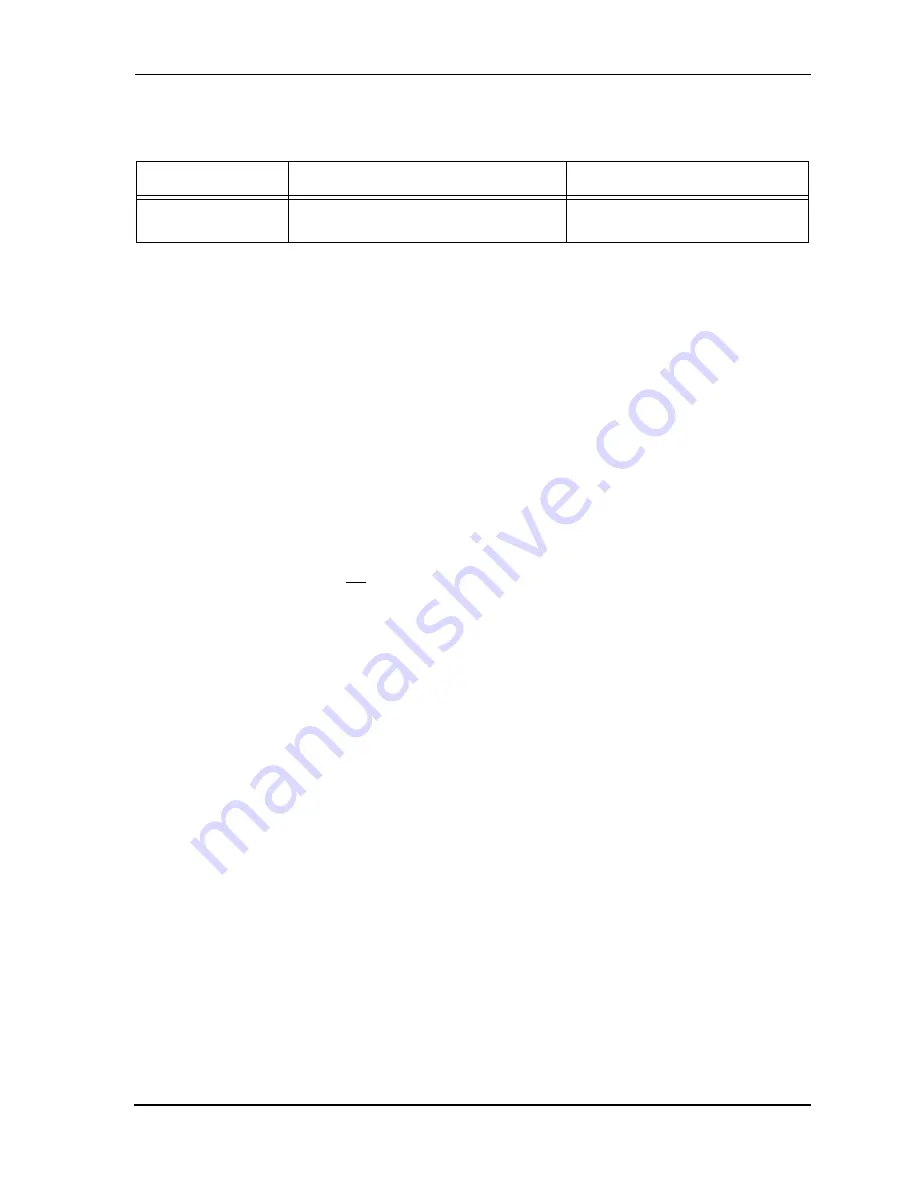

11

Receive FIFO full

Receive Overrun Error

HRFF = 1 and HROE = 0

HROE = 1

Table 9-6 HCSR Receive Interrupt Enable Bits

HRIE[1:0]

Interrupt

Condition

Summary of Contents for DSP56367

Page 16: ...xvi MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 22: ...xxii MOTOROLA List of Figures Figure Number Title Page Number ...

Page 26: ...xxvi MOTOROLA List of Tables Table Number Title Page Number ...

Page 148: ...4 6 DSP56367 MOTOROLA Design Considerations PLL Performance Issues ...

Page 248: ...9 30 DSP56367 MOTOROLA Serial Host Interface SHI Programming Considerations ...

Page 306: ...10 58 DSP56367 MOTOROLA Enhanced Serial Audio Interface ESAI ESAI Initialization Examples ...

Page 389: ...Bootstrap ROM Contents MOTOROLA DSP56367 A 15 end ...

Page 390: ...A 16 DSP56367 MOTOROLA Bootstrap ROM Contents ...

Page 432: ...C 8 DSP56367 MOTOROLA JTAG BSDL ...

Page 484: ...D 52 DSP56367 MOTOROLA Programmer s Reference ...

Page 490: ...E 6 DSP56367 MOTOROLA Power Consumption Benchmark ...

Page 516: ...F 26 DSP56367 MOTOROLA IBIS Model ...

Page 522: ...Index 6 MOTOROLA Index ...

Page 523: ......