9-26

DSP56367

MOTOROLA

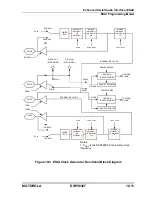

Serial Host Interface

SHI Programming Considerations

The HREQ output pin, if enabled for receive (HRQE[1:0] = 01), is asserted when the IOSR is

ready to receive and the HRX FIFO is not full; this operation guarantees that the next received

data word is stored in the FIFO. HREQ is deasserted at the first clock pulse of the next

received word. The HREQ line may be used to interrupt the external I

2

C master device.

Connecting the HREQ line between two SHI-equipped DSPs, one operating as an I

2

C master

device and the other as an I

2

C slave device, enables full hardware handshaking.

9.7.3.2

Transmit Data In I

2

C Slave Mode

A transmit session is initiated when the personal slave device address has been correctly

identified and the R/W bit of the received slave device address byte has been set. Following a

transmit initiation, the IOSR is loaded from HTX (assuming the latter was not empty) and its

contents are shifted out, MSB first, on the SDA line. Following each transmitted byte, the SHI

controller samples the SDA line at the ninth clock pulse, and inspects the ACK status. If the

transmitted byte was acknowledged (ACK = 0), the SHI controller continues and transmits the

next byte. However, if it was not acknowledged (ACK = 1), the transmit session is stopped

and the SDA line is released. Consequently, the external master device may generate a stop

event in order to terminate the session.

HTX contents are transferred to IOSR when the complete word (according to HM[1:0]) has

been shifted out. It is, therefore, the responsibility of the programmer to select the correct

number of bytes in an I

2

C frame so that they fit in a complete number of words. For this

purpose, the slave device address byte does not count as part of the data; therefore, it is treated

separately.

In a transmit session, only the transmit path is enabled and the IOSR-to-HRX FIFO transfers

are inhibited. When the HTX transfers its valid data word to IOSR, the HTDE status bit is set

and the DSP may write a new data word to HTX with either DSP instructions or DMA

transfers.

If HCKFR is cleared and both IOSR and HTX are empty when the master device attempts a

transmit session, an underrun condition occurs, setting the HTUE status bit, and the previous

word is retransmitted.

If HCKFR is set and both IOSR and HTX are empty when the master device attempts a

transmit session, the SHI holds the clock line to GND to avoid an underrun condition.

The HREQ output pin, if enabled for transmit (HRQE[1:0] = 10), is asserted when HTX is

transferred to IOSR for transmission. When asserted, HREQ indicates that the slave device is

ready to transmit the next data word. HREQ is deasserted at the first clock pulse of the next

transmitted data word. The HREQ line may be used to interrupt the external I

2

C master

device. Connecting the HREQ line between two SHI-equipped DSPs, one operating as an I

2

C

master device and the other as an I

2

C slave device, enables full hardware handshaking.

Summary of Contents for DSP56367

Page 16: ...xvi MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 22: ...xxii MOTOROLA List of Figures Figure Number Title Page Number ...

Page 26: ...xxvi MOTOROLA List of Tables Table Number Title Page Number ...

Page 148: ...4 6 DSP56367 MOTOROLA Design Considerations PLL Performance Issues ...

Page 248: ...9 30 DSP56367 MOTOROLA Serial Host Interface SHI Programming Considerations ...

Page 306: ...10 58 DSP56367 MOTOROLA Enhanced Serial Audio Interface ESAI ESAI Initialization Examples ...

Page 389: ...Bootstrap ROM Contents MOTOROLA DSP56367 A 15 end ...

Page 390: ...A 16 DSP56367 MOTOROLA Bootstrap ROM Contents ...

Page 432: ...C 8 DSP56367 MOTOROLA JTAG BSDL ...

Page 484: ...D 52 DSP56367 MOTOROLA Programmer s Reference ...

Page 490: ...E 6 DSP56367 MOTOROLA Power Consumption Benchmark ...

Page 516: ...F 26 DSP56367 MOTOROLA IBIS Model ...

Page 522: ...Index 6 MOTOROLA Index ...

Page 523: ......