10-24

DSP56367

MOTOROLA

Enhanced Serial Audio Interface (ESAI)

ESAI Programming Model

10.3.2.12

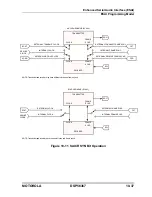

TCR Transmit Frame Sync Relative Timing (TFSR) - Bit 16

TFSR determines the relative timing of the transmit frame sync signal as referred to the serial

data lines, for a word length frame sync only (TFSL=0). When TFSR is cleared the word

length frame sync occurs together with the first bit of the data word of the first slot. When

TFSR is set the word length frame sync starts one serial clock cycle earlier (i.e together with

the last bit of the previous data word).

10.3.2.13

TCR Transmit Zero Padding Control (PADC) - Bit 17

When PADC is cleared, zero padding is disabled. When PADC is set, zero padding is enabled.

PADC, in conjunction with the TWA control bit, determines the way that padding is done for

operating modes where the word length is less than the slot length. See the TWA bit

description in Section 10.3.2.8, “TCR Transmit Word Alignment Control (TWA) - Bit 7” for

more details.

Since the data word is shorter than the slot length, the data word is extended until achieving

the slot length, according to the following rule:

1. If the data word is left-aligned (TWA=0), and zero padding is disabled (PADC=0),

then the last data bit is repeated after the data word has been transmitted. If zero

padding is enabled (PADC=1), zeroes are transmitted after the data word has been

transmitted.

2. If the data word is right-aligned (TWA=1), and zero padding is disabled (PADC=0),

then the first data bit is repeated before the transmission of the data word. If zero

padding is enabled (PADC=1), zeroes are transmitted before the transmission of the

data word.

10.3.2.14

TCR Reserved Bit - Bits 18

This bit is reserved. It reads as zero, and it should be written with zero for future

compatibility.

10.3.2.15

TCR Transmit Section Personal Reset (TPR) - Bit 19

The TPR control bit is used to put the transmitter section of the ESAI in the personal reset

state. The receiver section is not affected. When TPR is cleared, the transmitter section may

operate normally. When TPR is set, the transmitter section enters the personal reset state

immediately. When in the personal reset state, the status bits are reset to the same state as after

hardware reset. The control bits are not affected by the personal reset state. The transmitter

data pins are tri-stated while in the personal reset state; if a stable logic level is desired, the

transmitter data pins should be defined as GPIO outputs, or external pull-up or pull-down

resistors should be used. The transmitter clock outputs drive zeroes while in the personal reset

state. Note that to leave the personal reset state by clearing TPR, the procedure described in

Section 10.6, “ESAI Initialization Examples” should be followed.

Summary of Contents for DSP56367

Page 16: ...xvi MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 22: ...xxii MOTOROLA List of Figures Figure Number Title Page Number ...

Page 26: ...xxvi MOTOROLA List of Tables Table Number Title Page Number ...

Page 148: ...4 6 DSP56367 MOTOROLA Design Considerations PLL Performance Issues ...

Page 248: ...9 30 DSP56367 MOTOROLA Serial Host Interface SHI Programming Considerations ...

Page 306: ...10 58 DSP56367 MOTOROLA Enhanced Serial Audio Interface ESAI ESAI Initialization Examples ...

Page 389: ...Bootstrap ROM Contents MOTOROLA DSP56367 A 15 end ...

Page 390: ...A 16 DSP56367 MOTOROLA Bootstrap ROM Contents ...

Page 432: ...C 8 DSP56367 MOTOROLA JTAG BSDL ...

Page 484: ...D 52 DSP56367 MOTOROLA Programmer s Reference ...

Page 490: ...E 6 DSP56367 MOTOROLA Power Consumption Benchmark ...

Page 516: ...F 26 DSP56367 MOTOROLA IBIS Model ...

Page 522: ...Index 6 MOTOROLA Index ...

Page 523: ......