Enhanced Serial Audio Interface (ESAI)

Operating Modes

MOTOROLA

DSP56367

10-51

used in time division multiplexed (TDM) networks of codecs, DSPs with multiple words per

frame, or multi-channel devices.

Selecting the network mode and setting the frame rate divider to zero (DC=00000) selects the

on-demand mode. This special case does not generate a periodic frame sync. A frame sync

pulse is generated only when data is available to transmit. The on-demand mode requires that

the transmit frame sync be internal (output) and the receive frame sync be external (input).

Therefore, for simplex operation, the synchronous mode could be used; however, for

full-duplex operation, the asynchronous mode must be used. Data transmission that is data

driven is enabled by writing data into each TX. Although the ESAI is double buffered, only

one word can be written to each TX, even if the transmit shift register is empty. The receive

and transmit interrupts function as usual using TDE and RDF; however, transmit underruns

are impossible for on-demand transmission and are disabled.

10.4.4.2

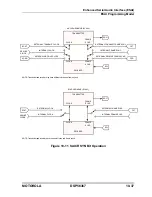

Synchronous/Asynchronous Operating Modes

The transmit and receive sections of the ESAI may be synchronous or asynchronous – i.e., the

transmitter and receiver sections may use common clock and synchronization signals

(synchronous operating mode),

or they may have their own separate clock and sync signals

(asynchronous operating mode). The SYN bit in the SAICR register selects synchronous or

asynchronous operation. Since the ESAI is designed to operate either synchronously or

asynchronously, separate receive and transmit interrupts are provided.

When SYN is cleared, the ESAI transmitter and receiver clocks and frame sync sources are

independent. If SYN is set, the ESAI transmitter and receiver clocks and frame sync come

from the transmitter section (either external or internal sources).

Data clock and frame sync signals can be generated internally by the DSP or may be obtained

from external sources. If internally generated, the ESAI clock generator is used to derive high

frequency clock, bit clock and frame sync signals from the DSP internal system clock.

10.4.4.3

Frame Sync Selection

The frame sync can be either a bit-long or word-long signal. The transmitter frame format is

defined by the TFSL bit in the TCR register. The receiver frame format is defined by the

RFSL bit in the RCR register.

1. In the word-long frame sync format, the frame sync signal is asserted during the entire

word data transfer period. This frame sync length is compatible with Motorola codecs,

SPI serial peripherals, serial A/D and D/A converters, shift registers, and

telecommunication PCM serial I/O.

2. In the bit-long frame sync format, the frame sync signal is asserted for one bit clock

immediately before the data transfer period. This frame sync length is compatible with

Intel and National components, codecs, and telecommunication PCM serial I/O.

Summary of Contents for DSP56367

Page 16: ...xvi MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 22: ...xxii MOTOROLA List of Figures Figure Number Title Page Number ...

Page 26: ...xxvi MOTOROLA List of Tables Table Number Title Page Number ...

Page 148: ...4 6 DSP56367 MOTOROLA Design Considerations PLL Performance Issues ...

Page 248: ...9 30 DSP56367 MOTOROLA Serial Host Interface SHI Programming Considerations ...

Page 306: ...10 58 DSP56367 MOTOROLA Enhanced Serial Audio Interface ESAI ESAI Initialization Examples ...

Page 389: ...Bootstrap ROM Contents MOTOROLA DSP56367 A 15 end ...

Page 390: ...A 16 DSP56367 MOTOROLA Bootstrap ROM Contents ...

Page 432: ...C 8 DSP56367 MOTOROLA JTAG BSDL ...

Page 484: ...D 52 DSP56367 MOTOROLA Programmer s Reference ...

Page 490: ...E 6 DSP56367 MOTOROLA Power Consumption Benchmark ...

Page 516: ...F 26 DSP56367 MOTOROLA IBIS Model ...

Page 522: ...Index 6 MOTOROLA Index ...

Page 523: ......