Timer/ Event Counter

Timer Modes of Operation

MOTOROLA

DSP56367

13-21

13.4.3

PULSE WIDTH MODULATION (PWM, MODE 7)

In this mode, the timer generates periodic pulses of a preset width. This function is available

only on timer 0.

Set the TE bit to clear the counter and enable the timer. The value the timer is to count is

loaded into the TPCR. When first timer clock is received from either the DSP56367 internal

clock divided by two (CLK/2) or the prescaler clock output, the counter is loaded with the

TLR value. Each subsequent timer clock increments the counter.

When the counter equals the value in the TCPR, the TIO0 output pin is toggled and the TCF

bit in the TCSR is set. The contents of the counter are placed into the TCR. If the TCIE bit is

set, a compare interrupt is generated. The counter continues to be incremented on each timer

clock.

If counter overflow has occurred, the TIO0 output pin is toggled, the TOF bit in TCSR is set,

and an overflow interrupt is generated if the TOIE bit is set. If the TRM bit is set, the counter

is loaded with the TLR value on the next timer clock and the count is resumed. If the TRM bit

is cleared, the counter continues to be incremented on each timer clock.

This process is repeated until the timer is disabled by clearing the TE bit.

TIO0 signal polarity is determined by the value of the INV bit. When the counter is started by

setting the TE bit, the TIO0 signal assumes the value of the INV bit. On each subsequent

toggling of the TIO0 signal, the polarity of the TIO0 signal is reversed. For example, if the

INV bit is set, the TIO0 signal generates the following signal: 1010. If the INV bit is cleared,

the TIO0 signal generates the following signal: 0101.

The counter contents can be read at any time by reading the TCR.

The value of the TLR determines the output period ($FFFFFF

−

TLR + 1). The timer counter

increments the initial TLR value and toggles the TIO0 signal when the counter value exceeds

$FFFFFF.

The duty cycle of the TIO0 signal is determined by the value in the TCPR. When the value in

the TLR is incremented to a value equal to the value in the TCPR, the TIO0 signal is toggled.

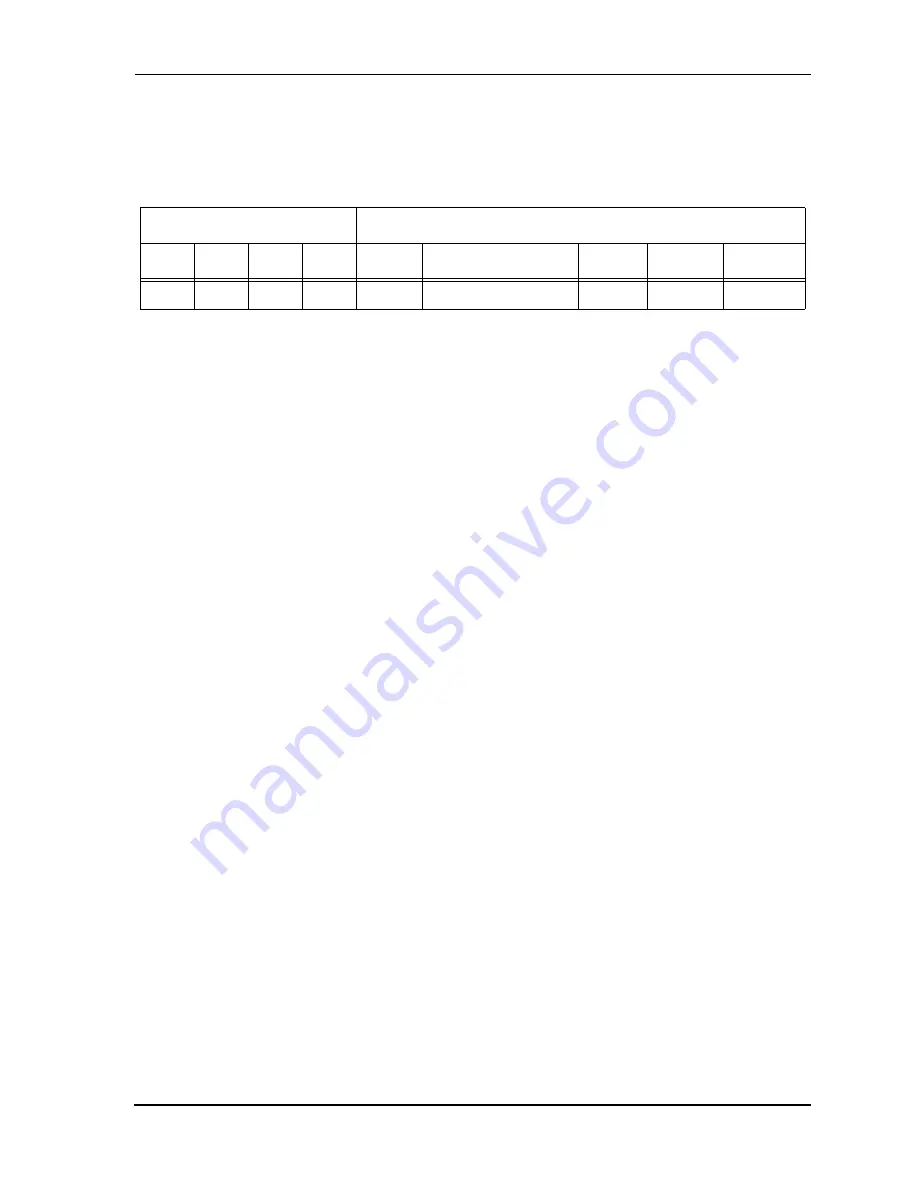

Bit Settings

Mode Characteristics

TC3

TC2

TC1

TC0

Mode

Name

Kind

TIO0

Clock

0

1

1

1

7

Pulse Width Modulation

PWM

Output

Internal

Summary of Contents for DSP56367

Page 16: ...xvi MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 22: ...xxii MOTOROLA List of Figures Figure Number Title Page Number ...

Page 26: ...xxvi MOTOROLA List of Tables Table Number Title Page Number ...

Page 148: ...4 6 DSP56367 MOTOROLA Design Considerations PLL Performance Issues ...

Page 248: ...9 30 DSP56367 MOTOROLA Serial Host Interface SHI Programming Considerations ...

Page 306: ...10 58 DSP56367 MOTOROLA Enhanced Serial Audio Interface ESAI ESAI Initialization Examples ...

Page 389: ...Bootstrap ROM Contents MOTOROLA DSP56367 A 15 end ...

Page 390: ...A 16 DSP56367 MOTOROLA Bootstrap ROM Contents ...

Page 432: ...C 8 DSP56367 MOTOROLA JTAG BSDL ...

Page 484: ...D 52 DSP56367 MOTOROLA Programmer s Reference ...

Page 490: ...E 6 DSP56367 MOTOROLA Power Consumption Benchmark ...

Page 516: ...F 26 DSP56367 MOTOROLA IBIS Model ...

Page 522: ...Index 6 MOTOROLA Index ...

Page 523: ......