2-8

DSP56367

MOTOROLA

Signal/Connection Descriptions

Interrupt and Mode Control

2.6

INTERRUPT AND MODE CONTROL

The interrupt and mode control signals select the chip’s operating mode as it comes out of

hardware reset. After RESET is deasserted, these inputs are hardware interrupt request lines.

BB

Input/

Output

Input

Bus Busy—BB is a bidirectional active-low input/output. BB indicates that the bus is

active. Only after BB is deasserted can the pending bus master become the bus master

(and then assert the signal again). The bus master may keep BB asserted after ceasing bus

activity regardless of whether BR is asserted or deasserted. This is called “bus parking”

and allows the current bus master to reuse the bus without rearbitration until another

device requires the bus. The deassertion of BB is done by an “active pull-up” method (i.e.,

BB is driven high and then released and held high by an external pull-up resistor).

For proper BB operation, the asynchronous bus arbitration enable bit (ABE) in the OMR

register must be set.

BB requires an external pull-up resistor.

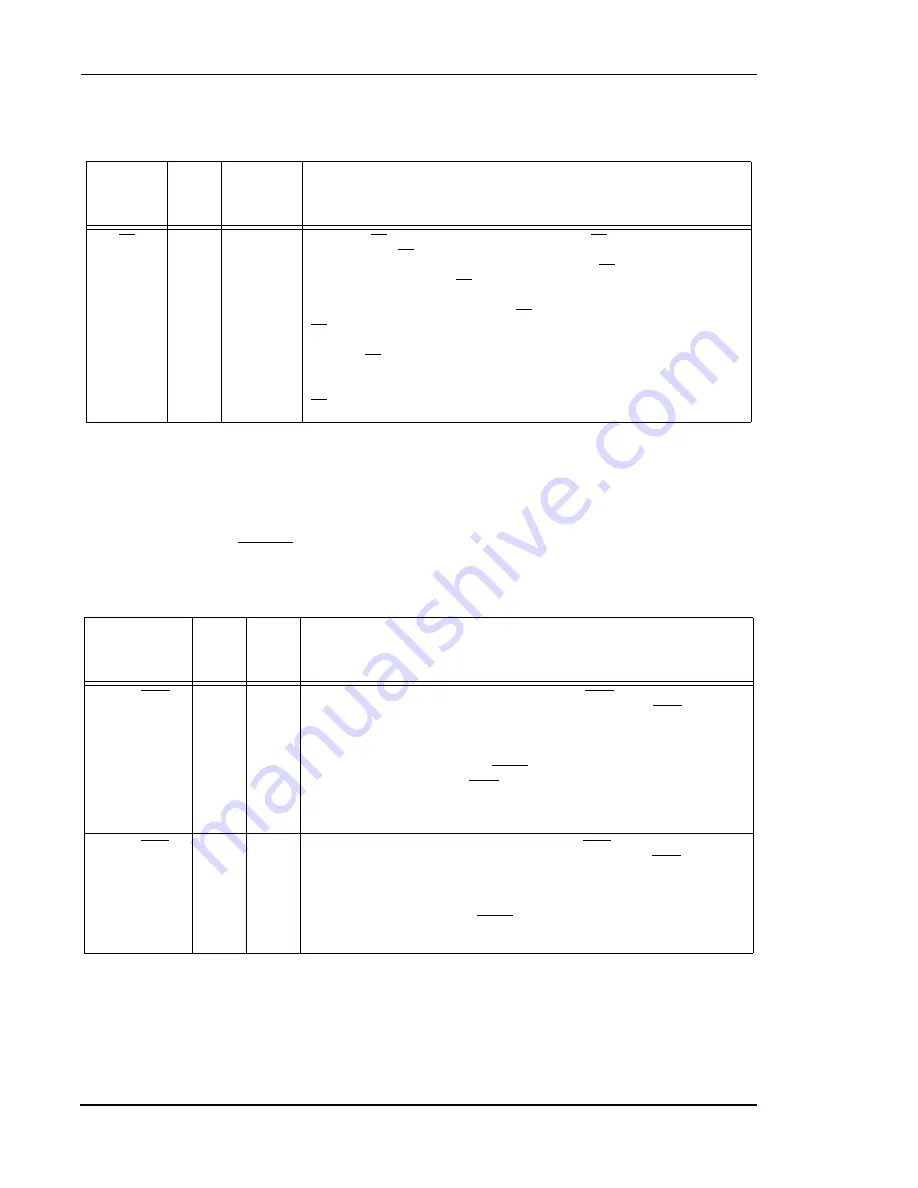

Table 2-8 Interrupt and Mode Control

Signal Name

Type

State

during

Reset

Signal Description

MODA/IRQA

Input

Input

Mode Select A/External Interrupt Request A—MODA/IRQA is an active-low

Schmitt-trigger input, internally synchronized to the DSP clock. MODA/IRQA selects the

initial chip operating mode during hardware reset and becomes a level-sensitive or

negative-edge-triggered, maskable interrupt request input during normal instruction

processing. MODA, MODB, MODC,

and MODD select one of 16 initial chip operating

modes, latched into the OMR when the RESET signal is deasserted. If the processor is in the

stop standby state and the MODA/IRQA pin is pulled to GND, the processor will exit the

stop state.

This input is 3.3V tolerant.

MODB/IRQB

Input

Input

Mode Select B/External Interrupt Request B—MODB/IRQB is an active-low

Schmitt-trigger input, internally synchronized to the DSP clock. MODB/IRQB selects the

initial chip operating mode during hardware reset and becomes a level-sensitive or

negative-edge-triggered, maskable interrupt request input during normal instruction

processing. MODA, MODB, MODC, and MODD select one of 16 initial chip operating

modes, latched into OMR when the RESET signal is deasserted.

This input is 3.3V tolerant.

Table 2-7 External Bus Control Signals (Continued)

Signal

Name

Type

State

during

Reset

Signal Description

Summary of Contents for DSP56367

Page 16: ...xvi MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 22: ...xxii MOTOROLA List of Figures Figure Number Title Page Number ...

Page 26: ...xxvi MOTOROLA List of Tables Table Number Title Page Number ...

Page 148: ...4 6 DSP56367 MOTOROLA Design Considerations PLL Performance Issues ...

Page 248: ...9 30 DSP56367 MOTOROLA Serial Host Interface SHI Programming Considerations ...

Page 306: ...10 58 DSP56367 MOTOROLA Enhanced Serial Audio Interface ESAI ESAI Initialization Examples ...

Page 389: ...Bootstrap ROM Contents MOTOROLA DSP56367 A 15 end ...

Page 390: ...A 16 DSP56367 MOTOROLA Bootstrap ROM Contents ...

Page 432: ...C 8 DSP56367 MOTOROLA JTAG BSDL ...

Page 484: ...D 52 DSP56367 MOTOROLA Programmer s Reference ...

Page 490: ...E 6 DSP56367 MOTOROLA Power Consumption Benchmark ...

Page 516: ...F 26 DSP56367 MOTOROLA IBIS Model ...

Page 522: ...Index 6 MOTOROLA Index ...

Page 523: ......