2 - 4

DSP96002 USER’S MANUAL

MOTOROLA

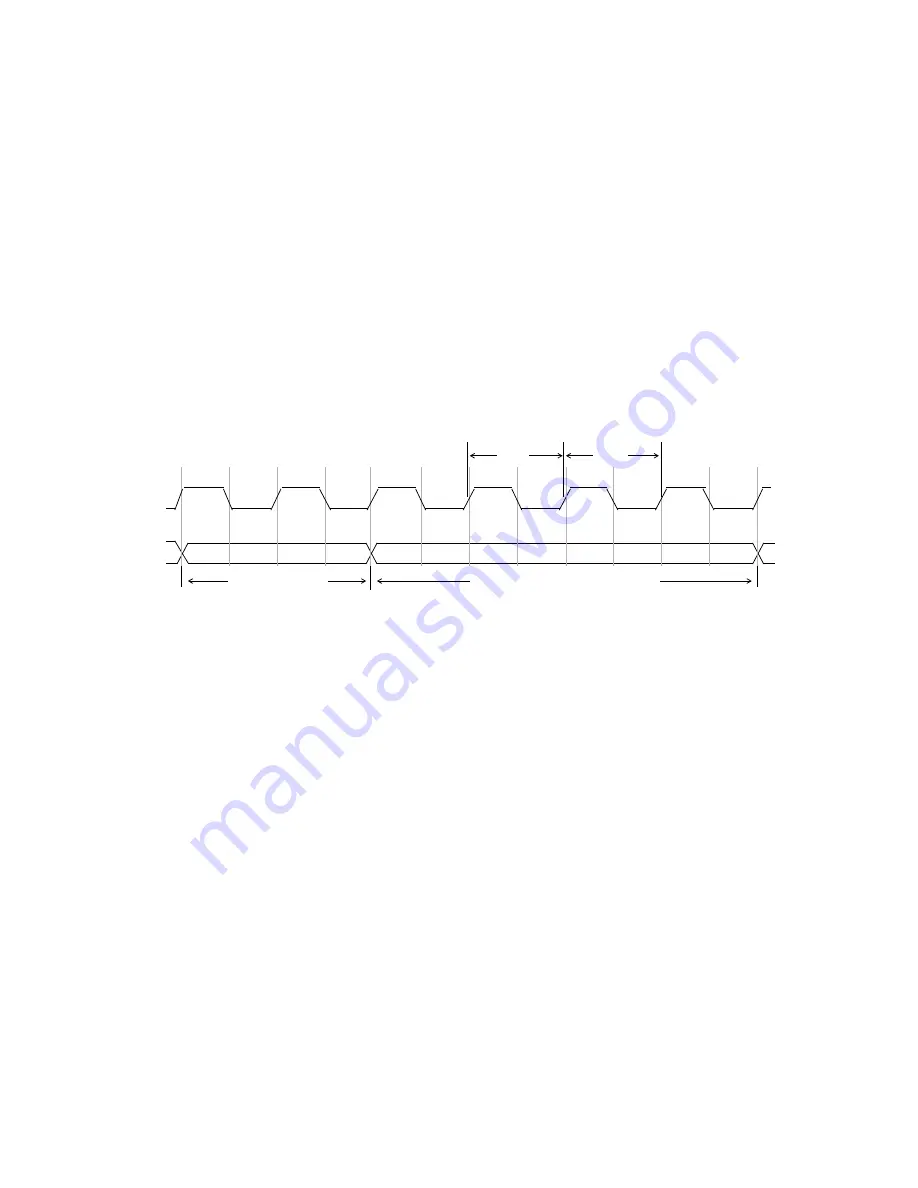

t0

t1

t2

t3

t0

t1

t2

tw

t2

tw

t2

t3

CLK

No Wait State

Instruction

Two Wait State Instruction

ing hardware reset and becomes a level sensitive or negative edge triggered, maskable

interrupt request input during normal instruction processing. MODA, MODB and MODC

select one of 8 initial chip operating modes, latched into the operating mode register

(OMR) when the

—

R

—

E

—

S

—

E

–

T pin is deasserted. If

—

I

—

R

—

Q

–

C is asserted syn-

chronous to the input clock (CLK), multiple processors can be resynchronized using the

WAIT instruction and asserting

—

I

—

R

—

Q

–

C to exit the wait state.

2.1.3 Power and Clock (39 Pins)

CLK

(Clock Input) - active high input, high frequency processor clock. Frequency is twice the

instruction rate. An internal phase generator divides CLK into four phases (t0, t1, t2 and

t3) which is the basic instruction execution cycle. Additional tw phases are optionally

generated to insert wait states (WS) into instruction execution. A wait state is formed by

pairing a t2 and tw phase. CLK should be continuous with a 46-54% duty cycle.

Quiet VCC (4)

(Power) - isolated power for the CPU logic. Must be tied to all other chip power pins ex-

ternally. User must provide adequate external decoupling capacitors.

Quiet VSS (4)

(Ground) - isolated ground for the CPU logic. Must be tied to all other chip ground pins

externally. User must provide adequate external decoupling capacitors.

Address Bus VCC(4)

(Power) - isolated power for sections of address bus I/O drivers. Must be tied to

all other chip power pins externally. User must provide adequate external decoupling

capacitors.

Address Bus VSS(8)

(Ground) - isolated ground for sections of address bus I/O drivers. Must be tied

to all other chip ground pins externally. User must provide adequate external decoupling

capacitors.

Data Bus VCC(4)

(Power) - isolated power for sections of data bus I/O drivers. Must be tied to all

other chip power pins externally. User must provide adequate external decoupling ca-

pacitors.

Data Bus VSS(8)

(Ground) - isolated ground for sections of data bus I/O drivers. Must be tied to

all other chip ground pins externally. User must provide adequate external decoupling

capacitors.

WS

WS

Summary of Contents for DSP96002

Page 3: ...1 2 DSP96002 USER S MANUAL MOTOROLA ...

Page 38: ...MOTOROLA DSP96002 USER S MANUAL 3 15 Figure 3 4 Modulo Arithmetic Unit Block Diagram ...

Page 39: ...3 16 DSP96002 USER S MANUAL MOTOROLA ...

Page 53: ...4 14 DSP96002 USER S MANUAL MOTOROLA ...

Page 76: ...MOTOROLA DSP96002 USER S MANUAL 5 23 Figure 5 8 Address Modifier Summary ...

Page 86: ...6 10 DSP96002 USER S MANUAL MOTOROLA ...

Page 101: ...MOTOROLA DSP96002 USER S MANUAL 7 15 Figure 7 9 HI Block Diagram One Port ...

Page 140: ...7 54 DSP96002 USER S MANUAL MOTOROLA ...

Page 166: ...9 10 DSP96002 USER S MANUAL MOTOROLA ...

Page 181: ...MOTOROLA DSP96002 USER S MANUAL 10 15 Figure 10 8 Program Address Bus FIFO ...

Page 337: ...MOTOROLA DSP96002 USER S MANUAL A 149 ...

Page 404: ...A 216 DSP96002 USER S MANUAL MOTOROLA PC xxxx D ...

Page 460: ...A 272 DSP96002 USER S MANUAL MOTOROLA SIOP Not affected ...

Page 484: ...A 296 DSP96002 USER S MANUAL MOTOROLA SSH PC SSL SR SP 1 SP ...

Page 519: ...MOTOROLA DSP96002 USER S MANUAL A 331 ...

Page 718: ...MOTOROLA DSP96002 USER S MANUAL B 199 ...

Page 871: ... MOTOROLA INC 1994 MOTOROLA TECHNICAL DATA SEMICONDUCTOR M Addendum ...

Page 888: ...MOTOROLA INDEX 1 INDEX ...

Page 889: ......