MOTOROLA

DSP96002 USER’S MANUAL

C-19

Note 1

The xx...xx pattern for the signaling NaNs indicates any NON-ZERO bit pattern.

Note 2

The xx...xx pattern for the non-signaling NaNs indicates any bit pattern. The DSP96002 gener-

ates all ones for QNaNs.

Note 3

If a register is written with a SNAN using a double precision floating-point move and then the

same register is read using single precision floating-point move the result will be a single preci-

sion SNAN (if the first 23 bits of the fraction are a non-zero pattern) or single precision infinity

(if the first 23 bits of the fraction are a zero pattern).

Note 4

The case when both U-TAG = 1 and V-TAG = 1 is reserved for future use.

C.1.5.1.2

RESULTS OF DATA ALU FLOATING-POINT OPERATIONS

This section describes how the Data ALU floating-point operation results are stored in the Data ALU regis-

ters.

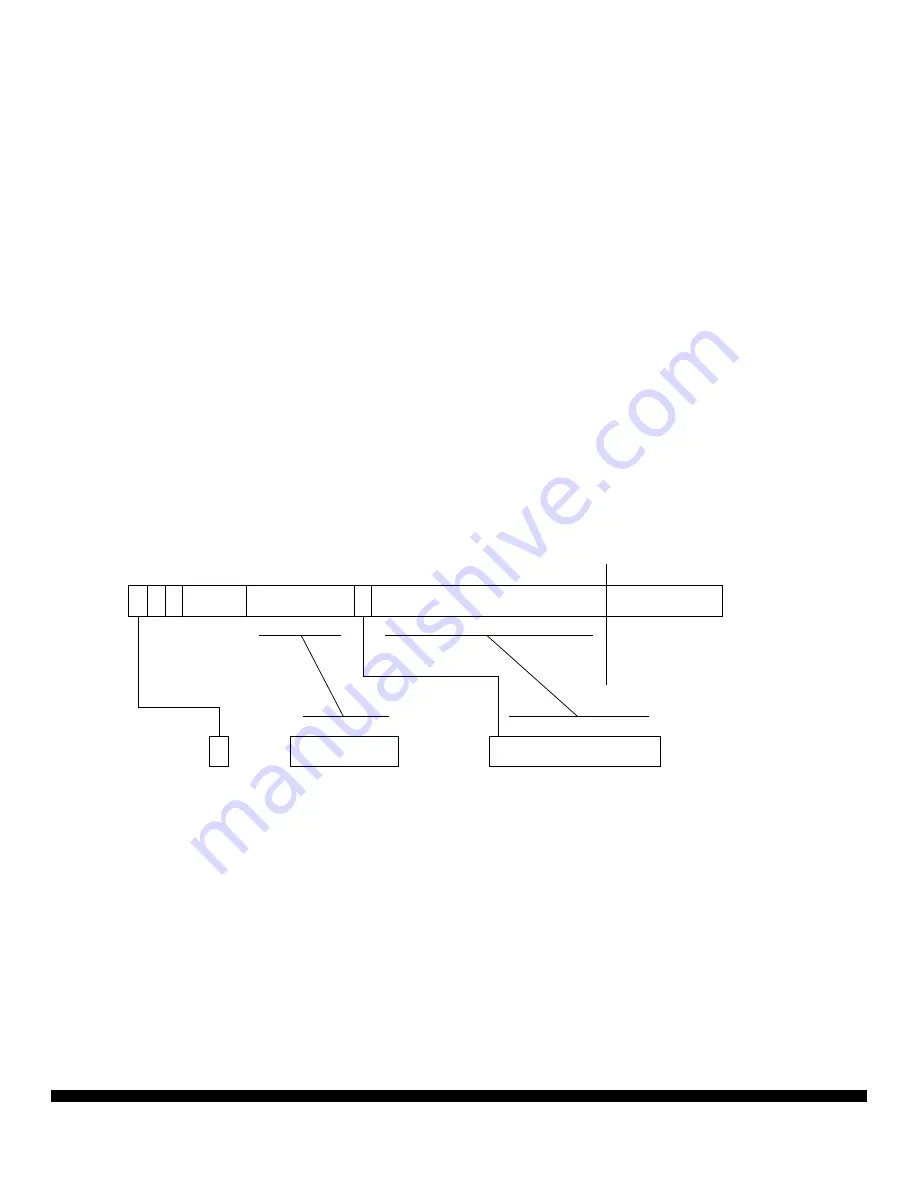

All DSP96002 Data ALU floating-point operations are executed in single extended precision, using single

extended precision input operands, and return single extended or single precision results in double pre-

cision format. The results are formatted in double precision before being stored in the Data ALU registers.

When performing a DP move into a register and then using that register in a DSP96002 SEP floating

point operation, the mantissa of the operand will be first truncated to a SEP value, as the hardware is

unable to operate on more than 32 mantissa bits. Figure C-13 explains how a DP register is used as

operand for a SEP operating unit (adder/multiplier).

The 11-bit exponent used by the SEP operating units is identical with the exponent of the original DP

number loaded into the register (both have the same bias, namely $3FF). This means that the number

can be used in computations directly, assuming that the least significant 21 mantissa bits are zero, oth-

erwise a round towards zero occurs because the mantissa is truncated to 32 bits (21 bits of the 52-bit

DP mantissa are ignored).

DP register

95 63 62 32 0

0 0 1 Zero 00000000000 0 0100 ..................00 0........ 00

\ / \ /

these bits

are ignored

/ \ / \

0 00000000000 0100 .......... 00

sign of the 11-bit exponent 32-bit mantissa

mantissa with 11-bit bias (1 bit integer

31 bits fraction)

Figure C-15. DP operand in a SEP operation

Note 4

Tags

Summary of Contents for DSP96002

Page 3: ...1 2 DSP96002 USER S MANUAL MOTOROLA ...

Page 38: ...MOTOROLA DSP96002 USER S MANUAL 3 15 Figure 3 4 Modulo Arithmetic Unit Block Diagram ...

Page 39: ...3 16 DSP96002 USER S MANUAL MOTOROLA ...

Page 53: ...4 14 DSP96002 USER S MANUAL MOTOROLA ...

Page 76: ...MOTOROLA DSP96002 USER S MANUAL 5 23 Figure 5 8 Address Modifier Summary ...

Page 86: ...6 10 DSP96002 USER S MANUAL MOTOROLA ...

Page 101: ...MOTOROLA DSP96002 USER S MANUAL 7 15 Figure 7 9 HI Block Diagram One Port ...

Page 140: ...7 54 DSP96002 USER S MANUAL MOTOROLA ...

Page 166: ...9 10 DSP96002 USER S MANUAL MOTOROLA ...

Page 181: ...MOTOROLA DSP96002 USER S MANUAL 10 15 Figure 10 8 Program Address Bus FIFO ...

Page 337: ...MOTOROLA DSP96002 USER S MANUAL A 149 ...

Page 404: ...A 216 DSP96002 USER S MANUAL MOTOROLA PC xxxx D ...

Page 460: ...A 272 DSP96002 USER S MANUAL MOTOROLA SIOP Not affected ...

Page 484: ...A 296 DSP96002 USER S MANUAL MOTOROLA SSH PC SSL SR SP 1 SP ...

Page 519: ...MOTOROLA DSP96002 USER S MANUAL A 331 ...

Page 718: ...MOTOROLA DSP96002 USER S MANUAL B 199 ...

Page 871: ... MOTOROLA INC 1994 MOTOROLA TECHNICAL DATA SEMICONDUCTOR M Addendum ...

Page 888: ...MOTOROLA INDEX 1 INDEX ...

Page 889: ......