MOTOROLA

M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL

3- 3

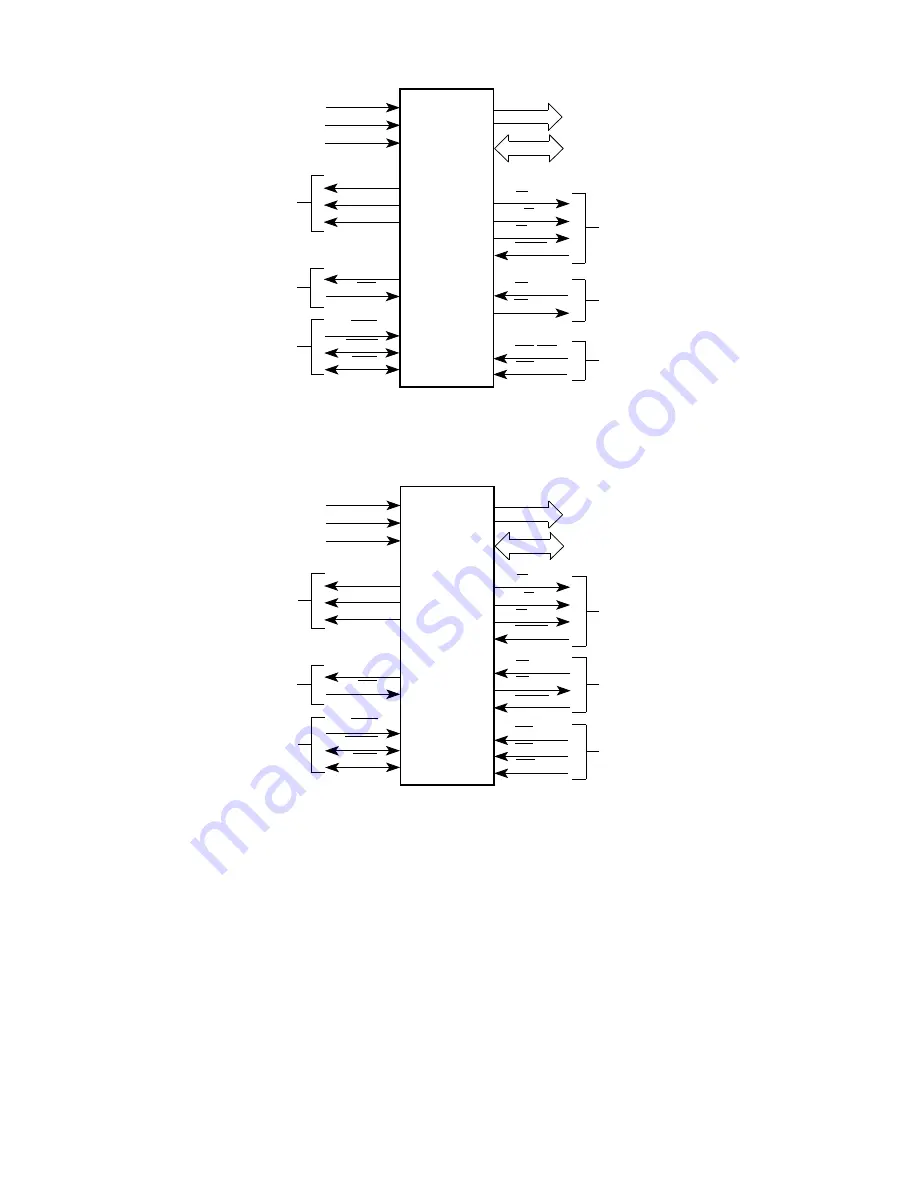

IPL2/IPL0

ADDRESS

BUS

A19–A0

DATA BUS

D7–D0

AS

R/W

DS

DTACK

BR

BG

IPL1

E

VPA

ASYNCHRONOUS

BUS

CONTROL

INTERRUPT

CONTROL

BUS

ARBITRATION

CONTROL

MC6800

PERIPHERAL

CONTROL

VCC(2)

GND(2)

CLK

FC0

FC1

FC2

BERR

RESET

HALT

PROCESSOR

STATUS

SYSTEM

CONTROL

MC6808

Figure 3-4. Input and Output Signals (MC68008, 48-Pin Version)

A21–A0

BGACK

IPL2

ADDRESS

BUS

DATA BUS

D7–D0

AS

R/W

DS

DTACK

BR

BG

IPL1

E

VPA

ASYNCHRONOUS

BUS

CONTROL

INTERRUPT

CONTROL

BUS

ARBITRATION

CONTROL

MC6800

PERIPHERAL

CONTROL

VCC

GND(2)

CLK

FC0

FC1

FC2

BERR

RESET

HALT

PROCESSOR

STATUS

SYSTEM

CONTROL

MC68008

IPL0

Figure 3-5. Input and Output Signals (MC68008, 52-Pin Version)

3.1

ADDRESS BUS (A23–A1)

This 23-bit, unidirectional, three-state bus is capable of addressing 16 Mbytes of data.

This bus provides the address for bus operation during all cycles except interrupt

acknowledge cycles and breakpoint cycles. During interrupt acknowledge cycles, address

lines A1, A2, and A3 provide the level number of the interrupt being acknowledged, and

address lines A23–A4 are driven to logic high.

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..