5- 16

M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL

MOTOROLA

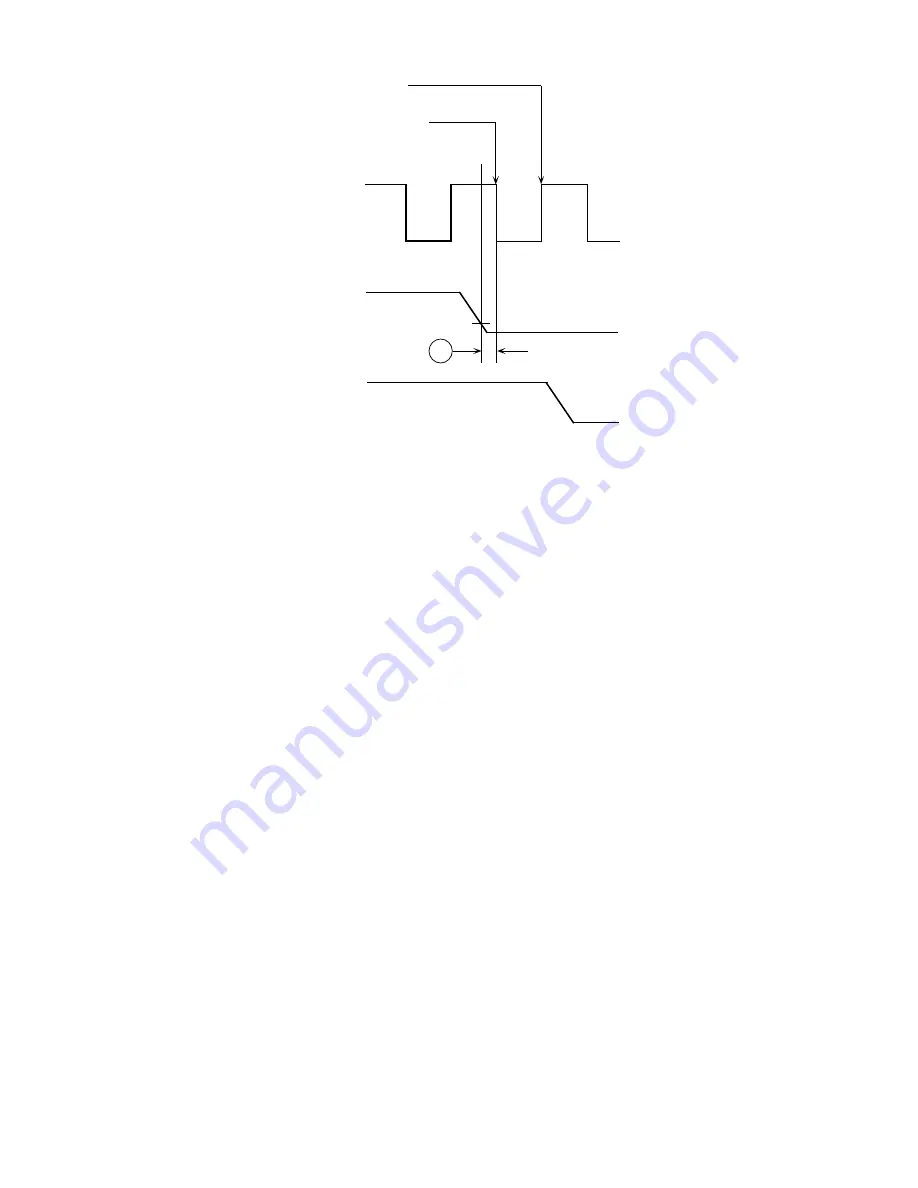

CLK

BR (EXTERNAL)

BR (iNTERNAL)

47

INTERNAL SIGNAL VALID

EXTERNAL SIGNAL SAMPLED

Figure 5-17. External Asynchronous Signal Synchronization

Bus arbitration control is implemented with a finite-state machine. State diagram (a) in

Figure 5-18 applies to all processors using 3-wire bus arbitration and state diagram (b)

applies to processors using 2-wire bus arbitration, in which

BGACK

is permanently

negated internally or externally. The same finite-state machine is used, but it is effectively

a two-state machine because

BGACK

is always negated.

In Figure 5-18, input signals R and A are the internally synchronized versions of

BR

and

BGACK

. The

BG

output is shown as G, and the internal three-state control signal is shown

as T. If T is true, the address, data, and control buses are placed in the high-impedance

state when

AS

is negated. All signals are shown in positive logic (active high), regardless

of their true active voltage level. State changes (valid outputs) occur on the next rising

edge of the clock after the internal signal is valid.

A timing diagram of the bus arbitration sequence during a processor bus cycle is shown in

Figure 5-19. The bus arbitration timing while the bus is inactive (e.g., the processor is

performing internal operations for a multiply instruction) is shown in Figure 5-20.

When a bus request is made after the MPU has begun a bus cycle and before

AS

has

been asserted (S0), the special sequence shown in Figure 5-21 applies. Instead of being

asserted on the next rising edge of clock,

BG

is delayed until the second rising edge

following its internal assertion.

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..