MEVB SUPPORT INFORMATION

M68MPB333UM/D

4-5

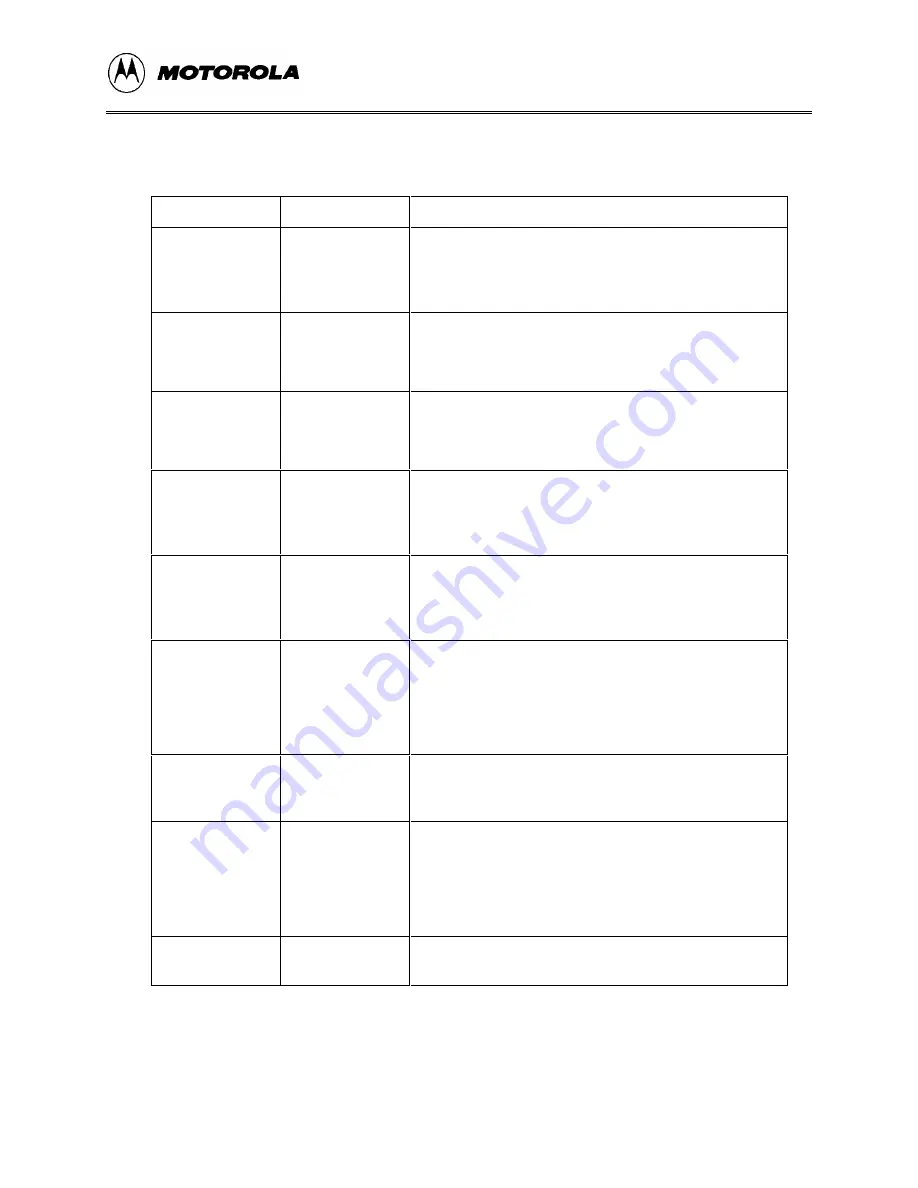

Table 4-6. Logic Analyzer Connector J12 Pin Assignments (continued)

Pin

Mnemonic

Signal

8

LAT-DSI /

(Latched

IFETCH)

LATCHED INSTRUCTION FETCH (INVERTED) –

Latched output signal of the inverted state of IFETCH

for CPU32-based MCUs; indicates instruction pipeline

activity.

9

DSO

DEVELOPMENT SERIAL OUT – Serial data output

signal for background debug mode.

INSTRUCTION PIPE for CPU32-based MCUs.

10

DSI

DEVELOPMENT SERIAL IN – Serial data input signal

for background debug mode.

INSTRUCTION FETCH for CPU32-based MCUs.

11

DSACK1

DATA AND SIZE ACKNOWLEDGE 1 – Active-low

input signal that allows asynchronous data transfers

and dynamic bus sizing between the MCU and external

devices.

12

DSACK0

DATA AND SIZE ACKNOWLEDGE 0 – Active-low

input signal that allows asynchronous data transfers

and dynamic bus sizing between the MCU and external

devices.

13

FC2 /

CS5

FUNCTION CODE 2 – Output signal that identifies the

processor state and address space of the current bus

cycle.

CHIP SELECT 5 – Output signal that selects peripheral

or memory devices at programmed addresses.

14

FC1

FUNCTION CODE 1 – Output signal that identifies the

processor state and address space of the current bus

cycle.

15

FC0 /

CS3

FUNCTION CODE 0 – Output signal that identifies the

processor state and address space of the current bus

cycle.

CHIP SELECT 3 – Output signal that selects peripheral

or memory devices at programmed addresses.

16

SIZ1

TRANSFER SIZE – Output signal that indicate the

number of bytes still to be transferred during this cycle.