68000 Motherboard User’s Manual

Rev. A

Page 38 of 54

A1JP340. The maximum hardware latency to the processor is the propagation delay of a

74

xx

74 and 74

xx

148 (13+19 ns typ., 25+30 ns max. at 25°C), plus one clock cycle.

The interrupt event latch may be cleared in software by disabling the corresponding

enable bit. The bit may subsequently be re-enabled to capture the next trigger event.

This sequence is used to acknowledge and reset from an interrupt event.

The on-board interrupt logic may be disabled from generating microprocessor interrupts

with the On-Board Interrupt Logic Enable jumper, A1JP310. This jumper is comprised

of three separate jumper connections for each of the individual /IPL

n

lines. The state of

the interrupt logic is available, regardless, on bits 0-2 of the Clock Synchronization

Register. Also, the /VPA generation for this function piggybacks on the Peripheral

Address Decoder and therefore requires A1JP270 be enabled.

7.14

On-Board Memory Banks 0/1

On-Board Banks support EPROM/SRAM devices according to jumper settings, per the

configuration outlined in Table 18 below. EPROM device support ranges from 2732

(4kB x 2 devices) through to 27512 (64kB x 2 devices). Note that the 2732 device is

shifted in the socket with the device’s pin 1 positioned in pin 3 of the socket. With all but

the 27512, address wrap-around aliasing occurs due to ignored address lines.

Both 0.3" and 0.6" DIP-24/28 devices are compatible with each Bank, depending on the

socket installed. The MSB devices, which reside at the lower memory addresses, occupy

IC351 for Bank 0 and IC361 for Bank 1. The LSB devices, at higher addresses, occupy

IC350/360. Bank 0 maps to the On-Board Block Address, ONBD_BASE, with an offset

of +$00000. Bank 1 maps with an offset of +$20000.

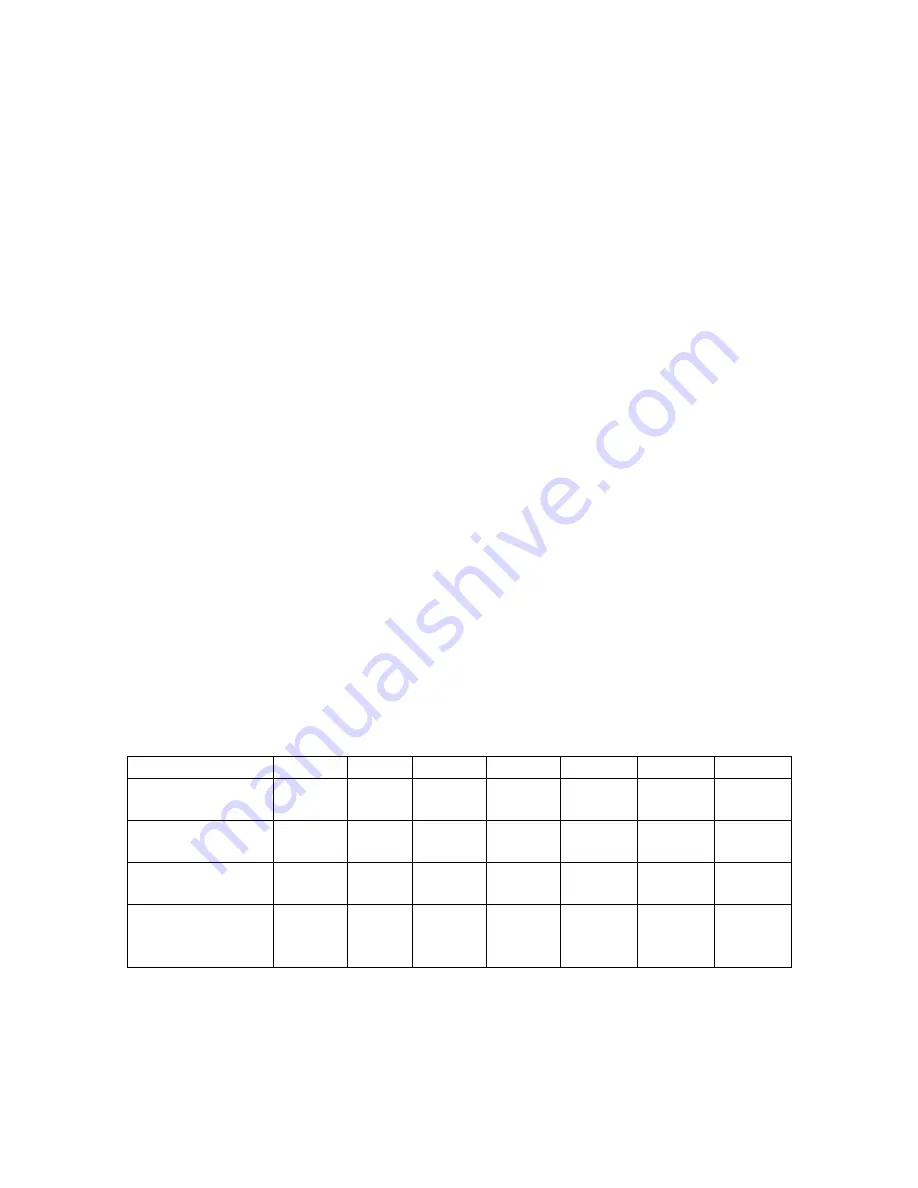

Table 18: On-Board Memory Banks’ Configuration

Jumper

6264

62256

2732

2764

27128

27256

27512

JP350, JP360

A16/VPP

open

3-4

(Pos 2)

open

1-2

(Pos 1)

1-2

(Pos 1)

1-2

(Pos 1)

5-6

(Pos 3)

JP351, JP361

A14/CS

1-2

2-3

1-2

open

2-3

2-3

2-3

JP352, JP362

A15/PGM

!!!

/WRL

!!!

3-4

(Pos 2)

3-4

(Pos 2)

open

1-2

(Pos 1)

1-2

(Pos 1)

5-6

(Pos 3)

5-6

(Pos 3)

JP353, JP363

A15/PGM

!!!

/WRU

!!!

3-4

(Pos 2)

3-4

(Pos 2)

open

1-2

(Pos 1)

1-2

(Pos 1)

5-6

(Pos 3)

5-6

(Pos 3)

Summary of Contents for MB68k-100

Page 1: ...Rev A Grant K c 2011 ...