68000 Motherboard User’s Manual

Rev. A

Page 44 of 54

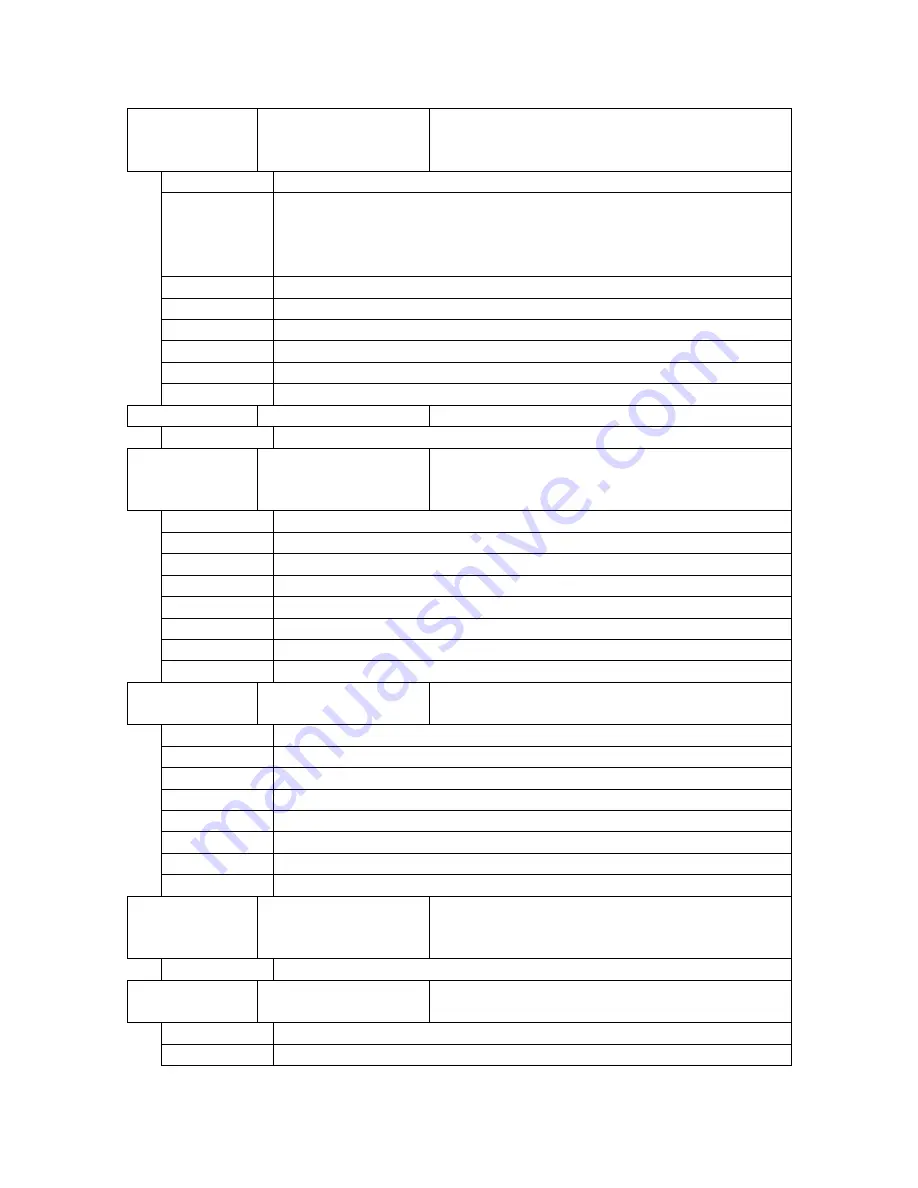

A1JP180

Start Vector Address

Selector

Presents byte value for reads of addresses 1 and

5 for specifying initial start address for

execution and supervisor stack pointer

Pos 1

Initial SSP/PC bit 16

Pos 2*

(0x00020000

for on-board

Bank 1)

Initial SSP/PC bit 17

Pos 3

Initial SSP/PC bit 18

Pos 4

Initial SSP/PC bit 19

Pos 5

Initial SSP/PC bit 20

Pos 6

Initial SSP/PC bit 21

Pos 7

Initial SSP/PC bit 22

Pos 8

Initial SSP/PC bit 23

A1JP181

SVS Enable

Enables the Start Vector Selector

1-2*

Enable

A1JP250

Automatic /DTACK

Address Blocks

Selector

Includes automatic bus cycle acknowledgement

for specified Block Addresses

Pos 1*

Include Block Address 0, /CS0

Pos 2

Include Block Address 1, /CS1

Pos 3

Include Block Address 2, /CS2

Pos 4

Include Block Address 3, /CS3

Pos 5

Include Block Address 4, /CS4

Pos 6

Include Block Address 5, /CS5

Pos 7

Include Block Address 6, /CS6

Pos 8

Include Block Address 7, /CS7

A1JP260

/DTACK Source

Selector

Selects M68k /DTACK control source

Pos 1*

Automatic acknowledgement from Automatic /DTACK Feedback

Pos 2

External /DTACK from Stack Connector

Pos 3

Automatic acknowledgement with 1 Wait State

Pos 4

Automatic acknowledgement with 2 Wait State

Pos 5

Automatic acknowledgement with 3 Wait State

Pos 6

Automatic acknowledgement with 4 Wait State

Pos 7

Automatic acknowledgement with 5 Wait State

Pos 8

Automatic acknowledgement with 9 Wait State

A1JP270

On-Board 6800

Peripheral Address

Decode Enable

Enables M68k /VPA control by the A23

address line

1-2*

Enable

A1JP280

On-Board Block

Address Selector

Selects Block Address for on-board peripheral

devices and memory banks

Pos 1*

Block Address 0, /CS0

Pos 2

Block Address 1, /CS1

Summary of Contents for MB68k-100

Page 1: ...Rev A Grant K c 2011 ...