MOTOROLA

M68020 USER’S MANUAL

6- 9

6.1.7 Trace Exception

To aid in program development, the M68000 processors include an instruction-by-

instruction tracing capability. The MC68020/EC020 can be programmed to trace all

instructions or only instructions that change program flow. In the trace mode, an

instruction generates a trace exception after it completes execution, allowing a debugger

program to monitor execution of a program.

The T1 and T0 bits in the supervisor portion of the SR control tracing. The state of these

bits when an instruction begins execution determines whether the instruction generates a

trace exception after the instruction completes. Clearing both the T1 and T0 bits disables

tracing, and instruction execution proceeds normally. Clearing the T1 bit and setting the

T0 bit causes an instruction that forces a change of flow to take a trace exception.

Instructions that increment the PC normally do not take the trace exception. Instructions

that are traced in this mode include all branches, jumps, instruction traps, returns, and

coprocessor instructions that modify the PC flow. This mode also includes SR

manipulations because the processor must re-prefetch instruction words to fill the pipe

again any time an instruction that can modify the SR is executed. The execution of the

BKPT instruction causes a change of flow if the opcode replacing the BKPT is an

instruction that causes a change of flow (i.e., a jump, branch, etc.). Setting the T1 bit and

clearing the T0 bit causes the execution of all instructions to force trace exceptions. Table

6-2 shows the trace mode selected by each combination of T1 and T0.

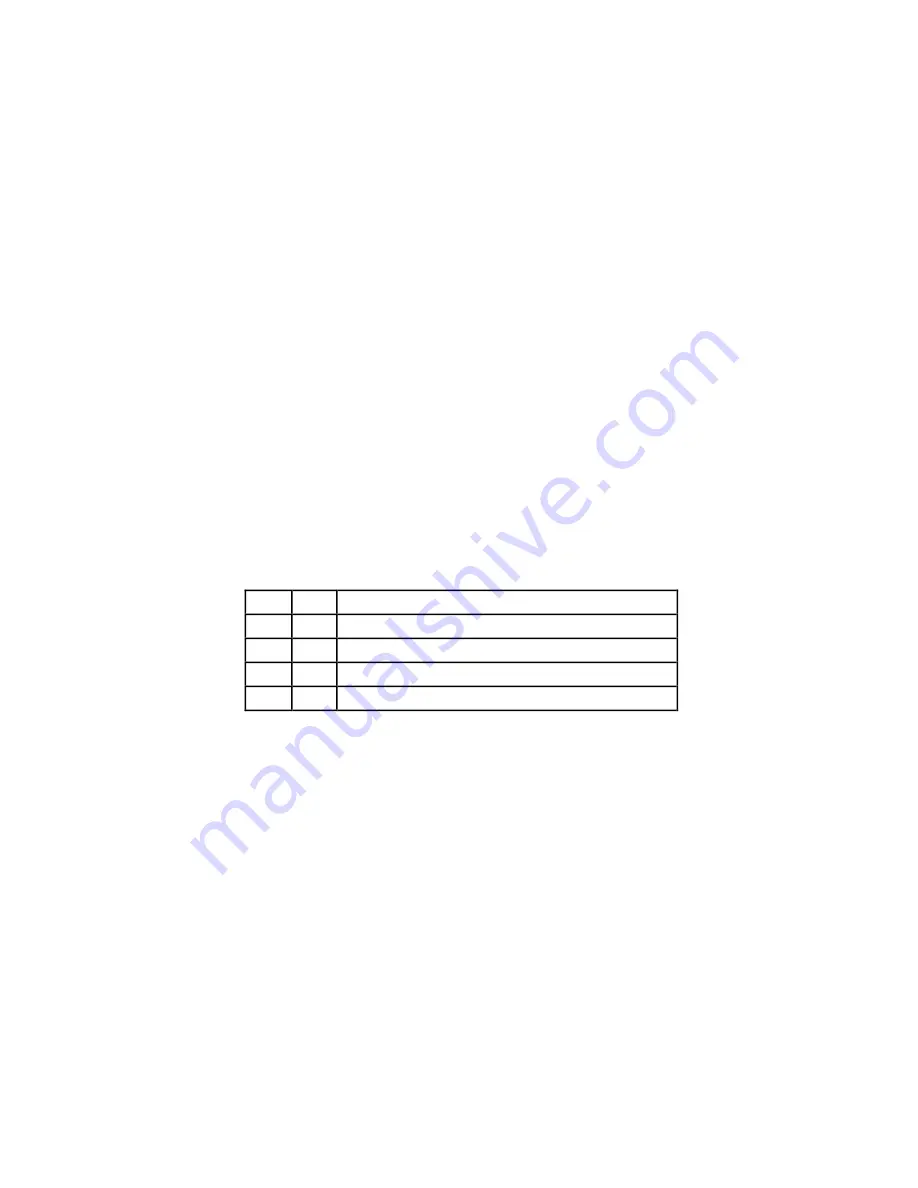

Table 6-2. Tracing Control

TI

T0

Tracing Function

0

0

No Tracing

0

1

Trace on Change of Flow (BRA, JMP, etc.)

1

0

Trace on Instruction Execution (Any Instruction)

1

1

Undefined, Reserved

In general terms, a trace exception is an extension to the function of any traced

instruction—i.e., the execution of a traced instruction is not complete until completion of

trace exception processing. If an instruction does not complete due to a bus error or

address error exception, trace exception processing is deferred until after the execution of

the suspended instruction is resumed, and the instruction execution completes normally. If

an interrupt is pending at the completion of an instruction, the trace exception processing

occurs before the interrupt exception processing starts. If an instruction forces an

exception as part of its normal execution, the forced exception processing occurs before

the trace exception is processed. See 6.1.11 Multiple Exceptions for a more complete

discussion of exception priorities.

When tracing is enabled and the processor attempts to execute an illegal or

unimplemented instruction, that instruction does not cause a trace exception since it is not

executed. This is of particular importance to an instruction emulation routine that performs

the instruction function, adjusts the stacked PC to skip the unimplemented instruction, and

returns. Before returning, the T1 and T0 bits of the SR on the stack should be checked. If

Summary of Contents for MC68020

Page 16: ...9 29 95 SECTION 1 OVERVIEW UM Rev 1 0 xx M68020 USER S MANUAL MOTOROLA ...

Page 268: ...MOTOROLA M68020 USER S MANUAL 9 13 Figure 9 9 Access Time Computation Diagram ...

Page 286: ...MOTOROLA M68020 USER S MANUAL 10 11 Figure 10 3 Read Cycle Timing Diagram ...

Page 287: ...10 12 M68020 USER S MANUAL MOTOROLA Figure 10 4 Write Cycle Timing Diagram ...

Page 288: ...MOTOROLA M68020 USER S MANUAL 10 13 Figure 10 5 Bus Arbitration Timing Diagram ...