MOTOROLA

M68020 USER’S MANUAL

7- 47

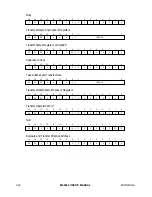

described in Section 6 Exception Processing. The vector number for the exception is

taken from the vector number field of the primitive, and the MC68020/EC020 uses the

four-word stack frame format shown in Figure 7-41.

0

11

12

15

STATUS REGISTER

0

0

0

0

VECTOR NUMBER

PROGRAM COUNTER

+06

+02

SP

Figure 7-41. MC68020/EC020 Preinstruction Stack Frame

The value of the PC saved in this stack frame is the F-line operation word address of the

coprocessor instruction during which the primitive was received. Thus, if the exception

handler routine does not modify the stack frame, an RTE instruction causes the

MC68020/EC020 to return and reinitiate execution of the coprocessor instruction.

The take preinstruction exception primitive can be used when the coprocessor does not

recognize a value written to either its command CIR or condition CIR to initiate a

coprocessor instruction. This primitive can also be used if an exception occurs in the

coprocessor instruction before any program-visible resources are modified by the

instruction operation. This primitive should not be used during a coprocessor instruction if

program-visible resources have been modified by that instruction. Otherwise, since the

MC68020/EC020 reinitiates the instruction when it returns from exception processing, the

restarted instruction receives the previously modified resources in an inconsistent state.

One of the most important uses of the take preinstruction exception primitive is to signal

an exception condition in a cpGEN instruction that was executing concurrently with the

main processor's instruction execution. If the coprocessor no longer requires the services

of the main processor to complete a cpGEN instruction and if the concurrent instruction

completion is transparent to the programming model, the coprocessor can release the

main processor by issuing a primitive with CA = 0. The main processor usually executes

the next instruction in the instruction stream, and the coprocessor completes its operations

concurrently with the main processor operation. If an exception occurs while the

coprocessor is executing an instruction concurrently, the exception is not processed until

the main processor attempts to initiate the next general or conditional instruction. After the

main processor writes to the command or condition CIR to initiate a general or conditional

instruction, it then reads the response CIR. At this time, the coprocessor can return the

take preinstruction exception primitive. This protocol allows the main processor to proceed

with exception processing related to the previous concurrently executing coprocessor

instruction and then return and reinitiate the coprocessor instruction during which the

exception was signaled. The coprocessor should record the addresses of all general

category instructions that can be executed concurrently with the main processor and that

support exception recovery. Since the exception is not reported until the next coprocessor

instruction is initiated, the processor usually requires the instruction address to determine

Summary of Contents for MC68020

Page 16: ...9 29 95 SECTION 1 OVERVIEW UM Rev 1 0 xx M68020 USER S MANUAL MOTOROLA ...

Page 268: ...MOTOROLA M68020 USER S MANUAL 9 13 Figure 9 9 Access Time Computation Diagram ...

Page 286: ...MOTOROLA M68020 USER S MANUAL 10 11 Figure 10 3 Read Cycle Timing Diagram ...

Page 287: ...10 12 M68020 USER S MANUAL MOTOROLA Figure 10 4 Write Cycle Timing Diagram ...

Page 288: ...MOTOROLA M68020 USER S MANUAL 10 13 Figure 10 5 Bus Arbitration Timing Diagram ...