4–4

M68020 USER’S MANUAL

MOTOROLA

F—Freeze Cache

The F-bit is set to freeze the instruction cache. When the F-bit is set and a cache miss

occurs, the entry (or line) is not replaced. When the F-bit is clear, a cache miss causes

the entry (or line) to be filled. A reset operation clears the F-bit.

E—Enable Cache

The E-bit is set to enable the instruction cache. When it is clear, the instruction cache is

disabled. A reset operation clears the E-bit. The supervisor normally enables the

instruction cache, but it can clear the E-bit for system debugging or emulation, as

required. Disabling the instruction cache does not flush the entries. If the cache is

reenabled, the previously valid entries remain valid and may be used.

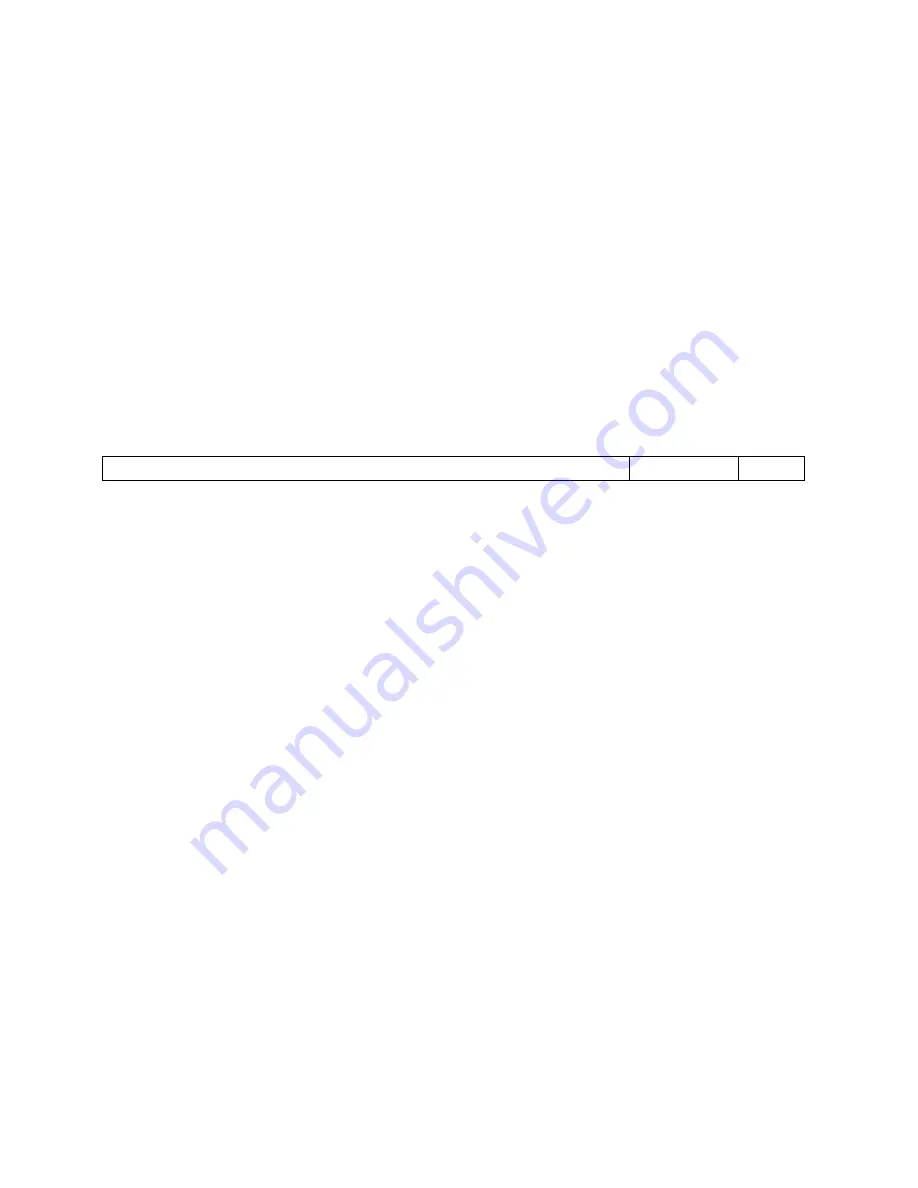

4.3.2 Cache Address Register (CAAR)

The format of the 32-bit CAAR is shown in Figure 4-3.

0

31

RESERVED

1

2

INDEX

7

8

RESERVED

Figure 4-3. Cache Address Register

Bits 31–8, 1, and 0—Reserved

These bits are reserved for use by Motorola.

Index Field

The index field contains the address for the “clear cache entry” operations. The bits of

this field, which correspond to A7–A2, specify the index and a long word of a cache line.

Summary of Contents for MC68020

Page 16: ...9 29 95 SECTION 1 OVERVIEW UM Rev 1 0 xx M68020 USER S MANUAL MOTOROLA ...

Page 268: ...MOTOROLA M68020 USER S MANUAL 9 13 Figure 9 9 Access Time Computation Diagram ...

Page 286: ...MOTOROLA M68020 USER S MANUAL 10 11 Figure 10 3 Read Cycle Timing Diagram ...

Page 287: ...10 12 M68020 USER S MANUAL MOTOROLA Figure 10 4 Write Cycle Timing Diagram ...

Page 288: ...MOTOROLA M68020 USER S MANUAL 10 13 Figure 10 5 Bus Arbitration Timing Diagram ...