MOTOROLA

M68020 USER’S MANUAL

5- 5

5.2 DATA TRANSFER MECHANISM

The MC68020/EC020 architecture supports byte, word, and long-word operands allowing

access to 8-, 16-, and 32-bit data ports through the use of asynchronous cycles controlled

by

DSACK1/DSACK0

. Byte, word, and long-word operands can be located on any byte

boundary, but misaligned transfers may require additional bus cycles, regardless of port

size.

5.2.1 Dynamic Bus Sizing

The MC68020/EC020 dynamically interprets the port size of the addressed device during

each bus cycle, allowing operand transfers to or from 8-, 16-, and 32-bit ports. During an

operand transfer cycle, the slave device signals its port size (byte, word, or long word) and

indicates completion of the bus cycle to the processor with the

DSACK1/DSACK0

signals.

Refer to Table 5-1 for

DSACK1/DSACK0

encodings and assertion results.

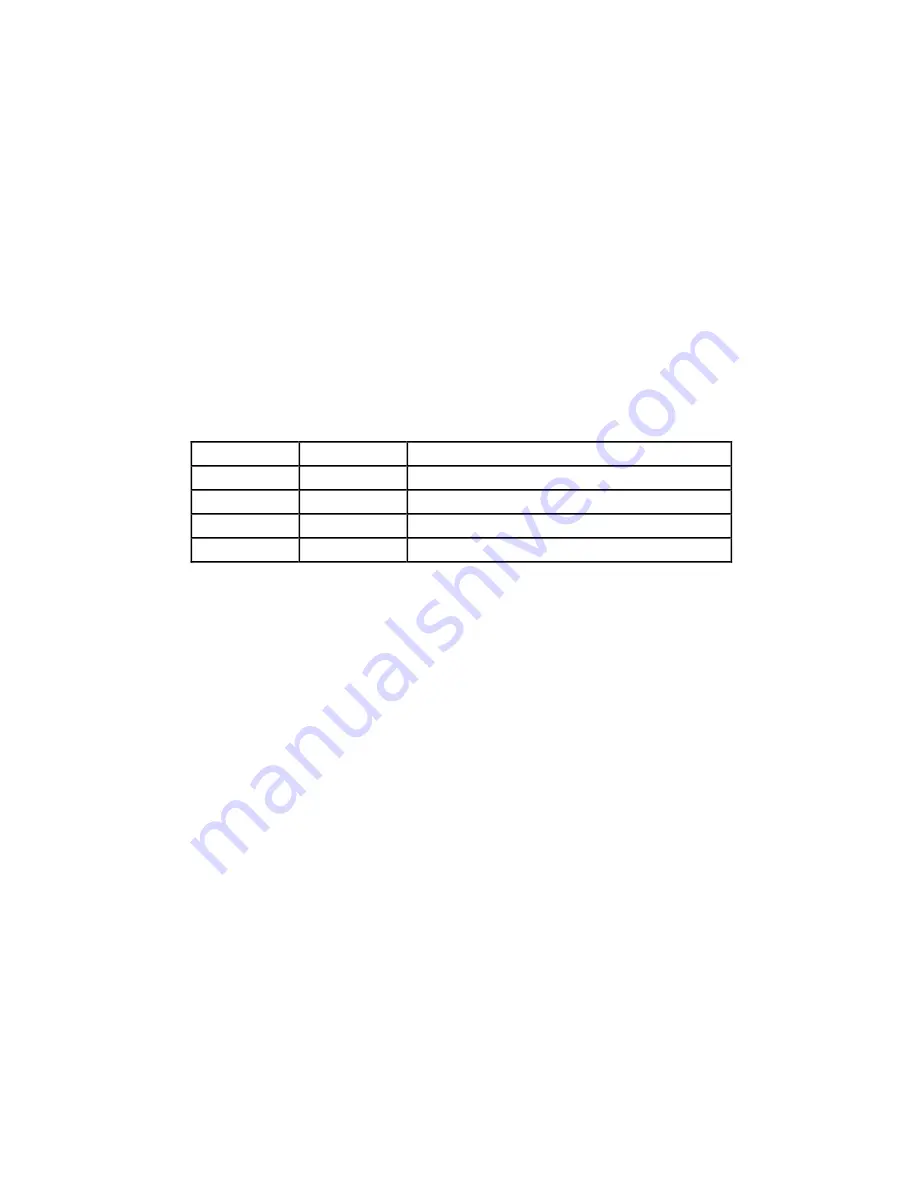

Table 5-1.

DSACK1/DSACK0

Encodings and Results

DSACK1

DSACK0

Result

Negated

Negated

Insert Wait States in Current Bus Cycle

Negated

Asserted

Complete Cycle—Data Bus Port Size is 8 Bits

Asserted

Negated

Complete Cycle—Data Bus Port Size is 16 Bits

Asserted

Asserted

Complete Cycle—Data Bus Port Size is 32 Bits

For example, if the processor is executing an instruction that reads a long-word operand

from a long-word-aligned address, it attempts to read 32 bits during the first bus cycle.

(Refer to 5.2.2 Misaligned Operands for the case of a word or byte address.) If the port

responds that it is 32 bits wide, the MC68020/EC020 latches all 32 bits of data and

continues with the next operation. If the port responds that it is 16 bits wide, the

MC68020/EC020 latches the 16 bits of valid data and runs another bus cycle to obtain the

other 16 bits. The operation for an 8-bit port is similar, but requires four read cycles. The

addressed device uses the

DSACK1/DSACK0

signals to indicate the port width. For

instance, a 32-bit device always returns

DSACK1/DSACK0

for a 32-bit port, regardless of

whether the bus cycle is a byte, word, or long-word operation.

Dynamic bus sizing requires that the portion of the data bus used for a transfer to or from

a particular port size be fixed. A 32-bit port must reside on D31–D0, a 16-bit port must

reside on D32–D16, and an 8-bit port must reside on D31–D24. This requirement

minimizes the number of bus cycles needed to transfer data to 8- and 16-bit ports and

ensures that the MC68020/EC020 correctly transfers valid data. The MC68020/EC020

always attempts to transfer the maximum amount of data on all bus cycles; for a long-

word operation, it always assumes that the port is 32 bits wide when beginning the bus

cycle.

The bytes of operands are designated as shown in Figure 5-3. The most significant byte of

a long-word operand is OP0; the least significant byte is OP3. The two bytes of a word-

length operand are OP2 (most significant) and OP3. The single byte of a byte-length

operand is OP3. These designations are used in the figures and descriptions that follow.

Summary of Contents for MC68020

Page 16: ...9 29 95 SECTION 1 OVERVIEW UM Rev 1 0 xx M68020 USER S MANUAL MOTOROLA ...

Page 268: ...MOTOROLA M68020 USER S MANUAL 9 13 Figure 9 9 Access Time Computation Diagram ...

Page 286: ...MOTOROLA M68020 USER S MANUAL 10 11 Figure 10 3 Read Cycle Timing Diagram ...

Page 287: ...10 12 M68020 USER S MANUAL MOTOROLA Figure 10 4 Write Cycle Timing Diagram ...

Page 288: ...MOTOROLA M68020 USER S MANUAL 10 13 Figure 10 5 Bus Arbitration Timing Diagram ...