4- 4

MC68306 USER'S MANUAL

MOTOROLA

4.3.2 Addressing Capabilities Summary

The EC000 core supports the basic addressing modes of the M68000 family. The register

indirect addressing modes support postincrement, predecrement, offset, and indexing,

which are particularly useful for handling data structures common to sophisticated

applications and high-level languages. The program counter indirect mode also has

indexing and offset capabilities. This addressing mode is typically required to support

position-independent software. Besides these addressing modes, the processor provides

index sizing and scaling features.

An instruction’s addressing mode can specify the value of an operand, a register

containing the operand, or how to derive the effective address of an operand in memory.

Each addressing mode has an assembler syntax. Some instructions imply the addressing

mode for an operand. These instructions include the appropriate fields for operands that

use only one addressing mode. Table 4-2 lists a summary of the effective addressing

modes for the processor. Refer to M68000PM/AD,

M68000 Family Programmer’s

Reference Manual, for details on instruction format and addressing modes.

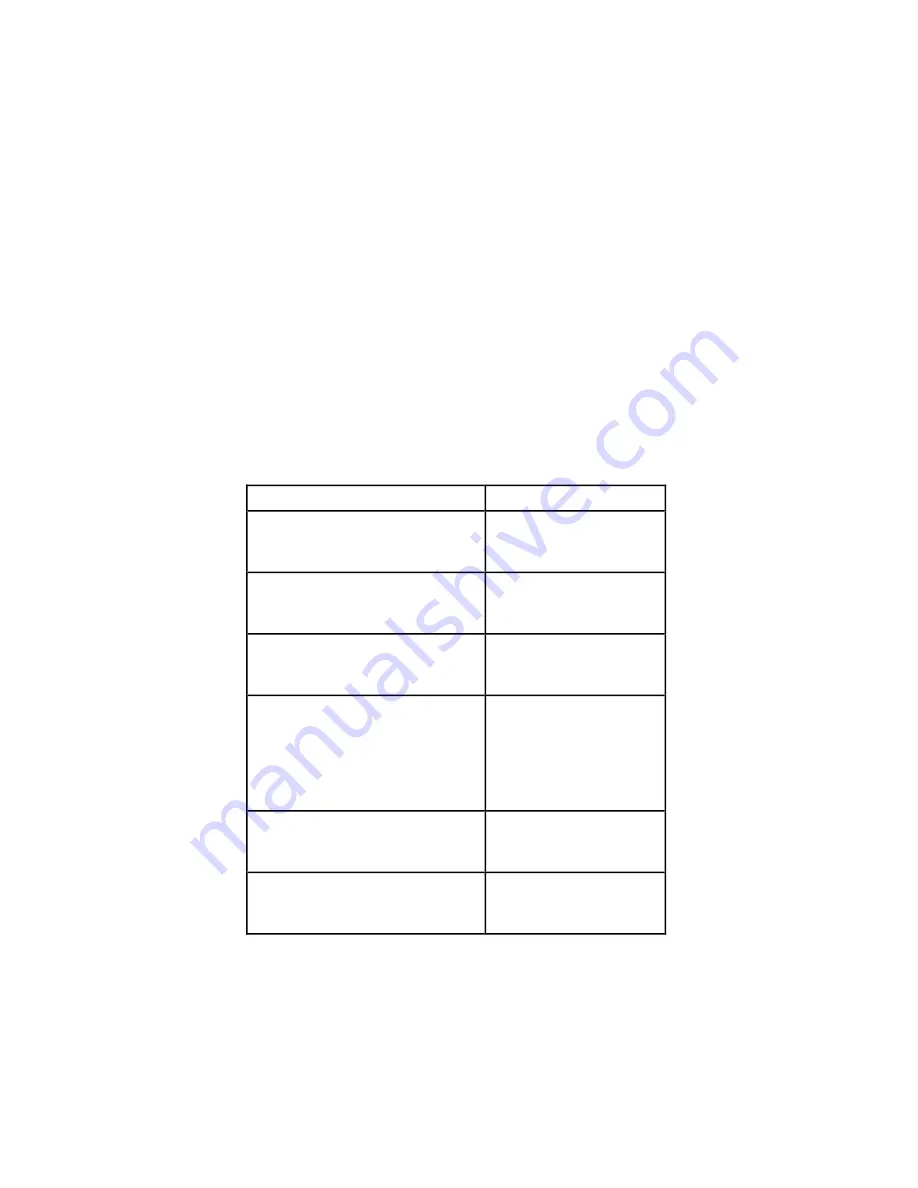

Table 4-2. Effective Addressing Modes

Addressing Modes

Syntax

Register Direct Addressing

Data Register Direct

Address Register Direct

EA=Dn

EA=An

Absolute Data Addressing

Absolute Short

Absolute Long

EA=(Next Word)

EA=(Next Two Words)

Program Counter Relative Addressing

Relative with Offset

Relative with Index and Offset

EA=(PC)+d16

EA=(PC)+d8

Register Indirect Addressing

Register Indirect

Postincrement Register Indirect

Predecrement Register Indirect

Register Indirect with Offset

Indexed Register Indirect with Offset

EA=(An)

EA=(An), An ¨ An+N

An ¨ An–N, EA=(An)

EA=(An)+d 16

EA=(An)+(Xn)+d 8

Immediate Data Addressing

Immediate

Quick Immediate

DATA=Next Word(s)

Inherent Data

Implied Addressing

Implied Register

EA=SR, USP, SSP, PC,

VBR, SFC, DFC