MOTOROLA

MC68838 USER’S MANUAL

9- 1

SECTION 9

CAM INTERFACE OPERATION

The CAM interface provides actuation and data signals to an FSI CAM, a separate CAM,

or other frame recognition logic used for 48-bit destination and/or source address

recognition. Outputs from the MAC-CAM interface consist of the RCDATx, DA, and

LDADDR signals. The match input to the MAC from the CAM is the

MATCH, TR

—

BR

—

FWD, RABORT or RABORT2 signals. All signals are described and synchronized relative

to the BYTCLK signal provided by the FCG.

This section is written for ease of explanation from the point of view that the address

recognition logic consists mainly of a content addressable memory array. However, any

recognition logic may be employed that observes the signal requirements. The section

also refers mostly to a positive recognition logic implementation, i.e., an implementation

that asserts

MATCH on TR

—

BR

—

FWD to copy a frame when an address is recognized.

Another valid implementation is to put the MAC in a promiscuous copy mode, COPY

—

IND

—

LLC and COPY_GRP_LLC are set to one, and then assert RABORT or RABORT2

to not copy, or flush, frames whose addresses are recognized.

9.1 CAM INTERFACE OPERATION

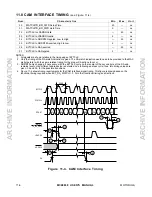

The CAM interface presents frame information to a CAM for comparison purposes one

byte at a time from the ELM chip over the RCDATx lines at the same time the information

is being furnished to the MAC. Since the byte-wide data on RCDATx is two data symbols,

only the lower four bits of each symbol need be used; the upper four bits of each symbol

are always zero for data. Thus, the CAM uses RCDAT8–RCDAT5 and RCDAT3–

RCDAT0.

If the presented information matches an address stored in the CAM, the

MATCH line to

the MAC should be asserted by the CAM. LDADDR and DA are additional signals driven

by the MAC that indicate to external logic or a CAM the position of data on the RCDATx

lines relative to the frame. BYTCLK and SYMCLK are used to clock the CAM interface and

to latch the address into the CAM.

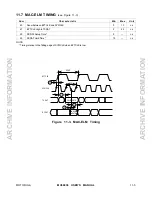

9.1.1 Normal (Nonextended) Match Mode

Referring to Figure 9-1, the following sequence of events should occur between the MAC

and a CAM when an address is presented on the RCDATx lines and the MAC has

EXT_DA_MATCH = 0 in control register B:

1. LDADDR is pulsed for one BYTCLK cycle just before the first byte of both the DA

and SA fields is given to the MAC and the CAM from the ELM. The DA signal from

the MAC differentiates whether the current address is the DA or SA. LDADDR is

ARCHIVE INFORMA

TION

ARCHIVE INFORMA

TION

Summary of Contents for MC68838

Page 20: ...2 8 MC68838 USER S MANUAL MOTOROLA ARCHIVE INFORMATION ARCHIVE INFORMATION ...

Page 63: ...5 4 MC68838 USER S MANUAL MOTOROLA ARCHIVE INFORMATION ARCHIVE INFORMATION ...

Page 65: ...6 2 MC68838 USER S MANUAL MOTOROLA ARCHIVE INFORMATION ARCHIVE INFORMATION ...

Page 82: ...9 6 MC68838 USER S MANUAL MOTOROLA ARCHIVE INFORMATION ARCHIVE INFORMATION ...

Page 86: ...10 4 MC68838 USER S MANUAL MOTOROLA ARCHIVE INFORMATION ARCHIVE INFORMATION ...

Page 98: ...12 6 MC68838 USER S MANUAL MOTOROLA ARCHIVE INFORMATION ARCHIVE INFORMATION ...