Low-Voltage Inhibit (LVI)

Functional Description

MC68HC908GP32

•

MC68HC08GP32

—

Rev. 6

Technical Data

MOTOROLA

Low-Voltage Inhibit (LVI)

191

An LVI reset also drives the RST pin low to provide low-voltage

protection to external peripheral devices.

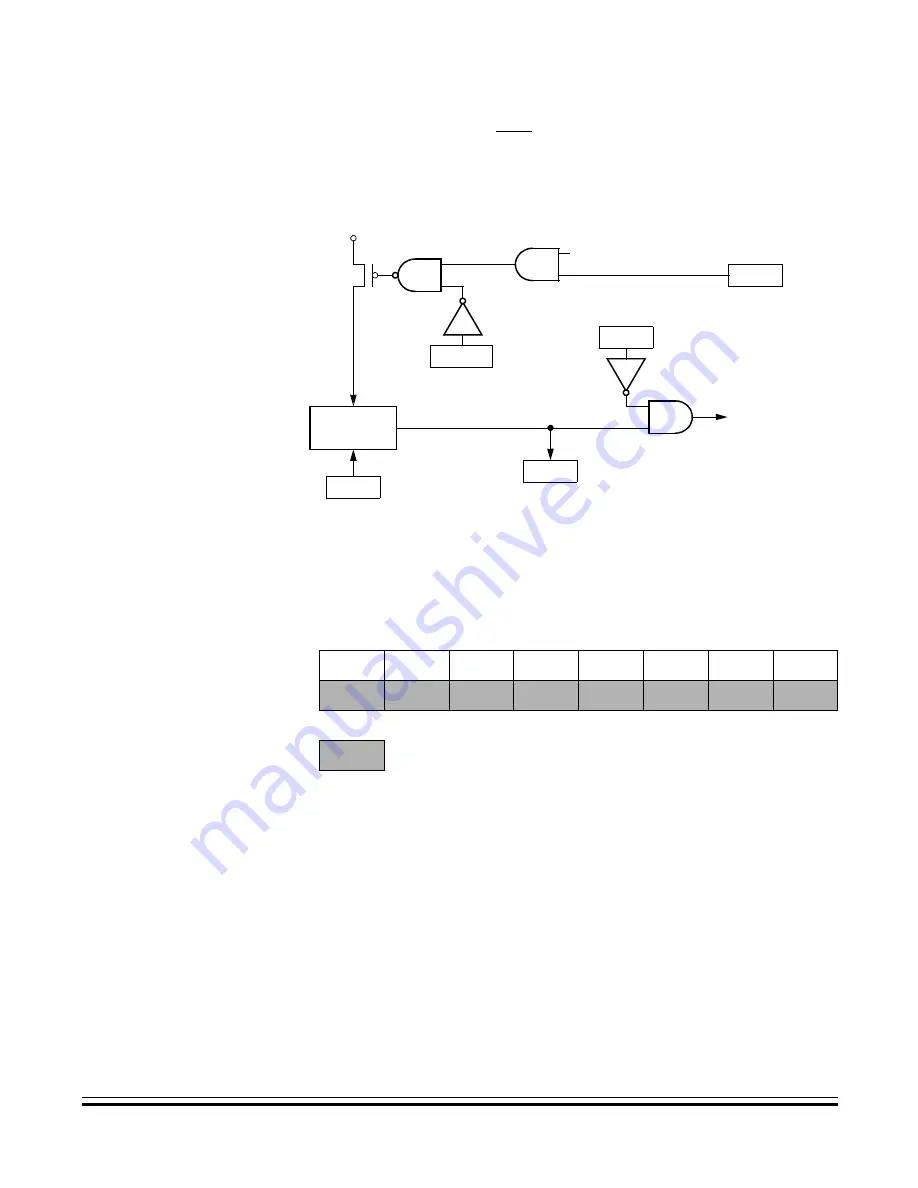

Figure 14-1. LVI Module Block Diagram

14.4.1 Polled LVI Operation

In applications that can operate at V

DD

levels below the V

TRIPF

level,

software can monitor V

DD

by polling the LVIOUT bit. In the configuration

register, the LVIPWRD bit must be at logic 0 to enable the LVI module,

and the LVIRSTD bit must be at logic 1 to disable LVI resets.

LOW V

DD

DETECTOR

LVIPWRD

STOP INSTRUCTION

LVISTOP

LVI RESET

LVIOUT

V

DD

> LVI

Trip

= 0

V

DD

≤

LVI

Trip

= 1

FROM CONFIG

FROM CONFIG1

V

DD

FROM CONFIG1

LVIRSTD

LVI5OR3

FROM CONFIG1

Addr.

Register Name

Bit 7

6

5

4

3

2

1

Bit 0

$FE0C

LVI Status Register

(LVISR)

Read: LVIOUT

0

0

0

0

0

0

0

Write:

Reset:

0

0

0

0

0

0

0

0

= Unimplemented

Figure 14-2. LVI I/O Register Summary

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..