Serial Communications Interface Module (SCI)

Functional Description

MC68HC908GP32

•

MC68HC08GP32

—

Rev. 6

Technical Data

MOTOROLA

Serial Communications Interface Module (SCI)

251

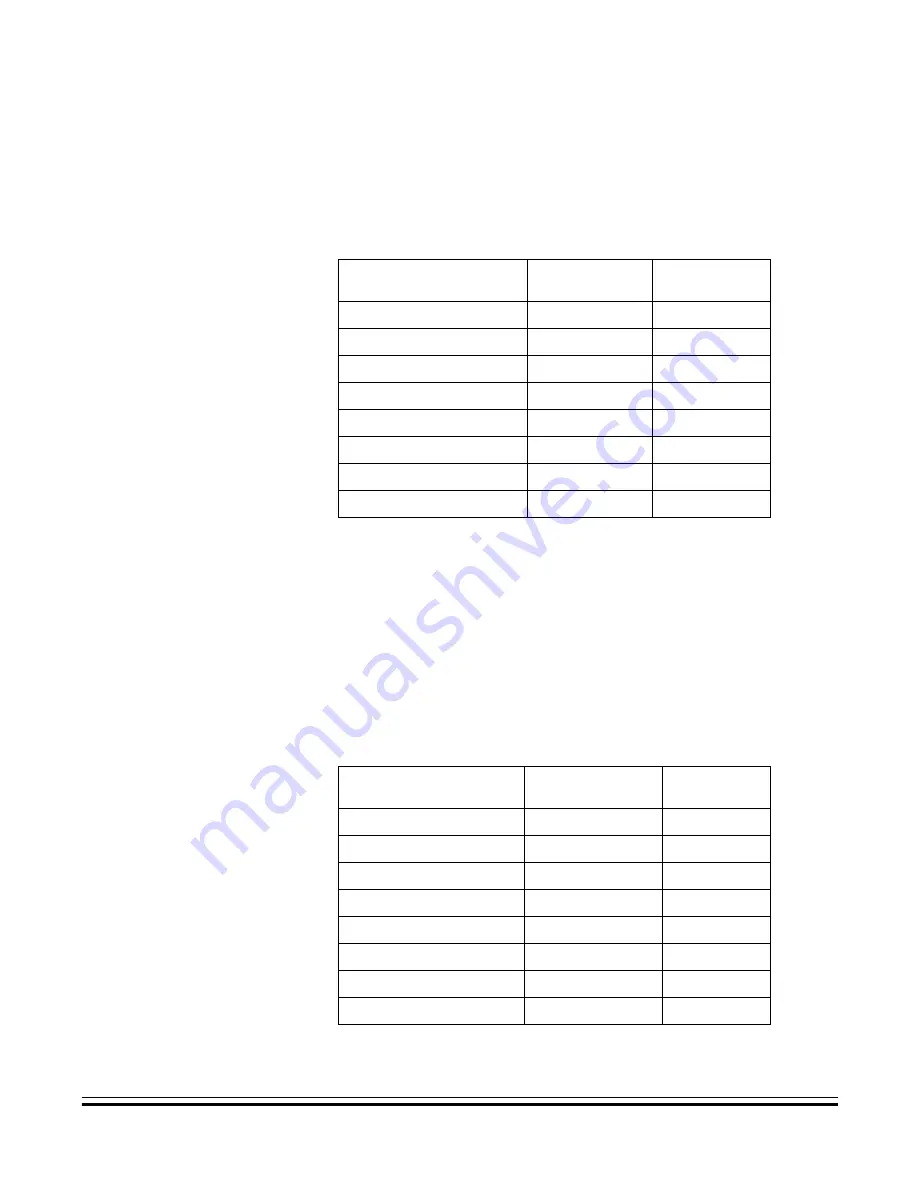

To verify the start bit and to detect noise, data recovery logic takes

samples at RT3, RT5, and RT7.

Table 18-2

summarizes the results of

the start bit verification samples.

Start bit verification is not successful if any two of the three verification

samples are logic 1s. If start bit verification is not successful, the RT

clock is reset and a new search for a start bit begins.

To determine the value of a data bit and to detect noise, recovery logic

takes samples at RT8, RT9, and RT10.

Table 18-3

summarizes the

results of the data bit samples.

Table 18-2. Start Bit Verification

RT3, RT5, and RT7

Samples

Start Bit

Verification

Noise Flag

000

Yes

0

001

Yes

1

010

Yes

1

011

No

0

100

Yes

1

101

No

0

110

No

0

111

No

0

Table 18-3. Data Bit Recovery

RT8, RT9, and RT10

Samples

Data Bit

Determination

Noise Flag

000

0

0

001

0

1

010

0

1

011

1

1

100

0

1

101

1

1

110

1

1

111

1

0

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..