Serial Peripheral Interface Module (SPI)

Error Conditions

MC68HC908GP32

•

MC68HC08GP32

—

Rev. 6

Technical Data

MOTOROLA

Serial Peripheral Interface Module (SPI)

317

interrupts share the same CPU interrupt vector.

(See

Figure 20-11

.) It is

not possible to enable MODF or OVRF individually to generate a

receiver/error CPU interrupt request. However, leaving MODFEN low

prevents MODF from being set.

If the CPU SPRF interrupt is enabled and the OVRF interrupt is not,

watch for an overflow condition.

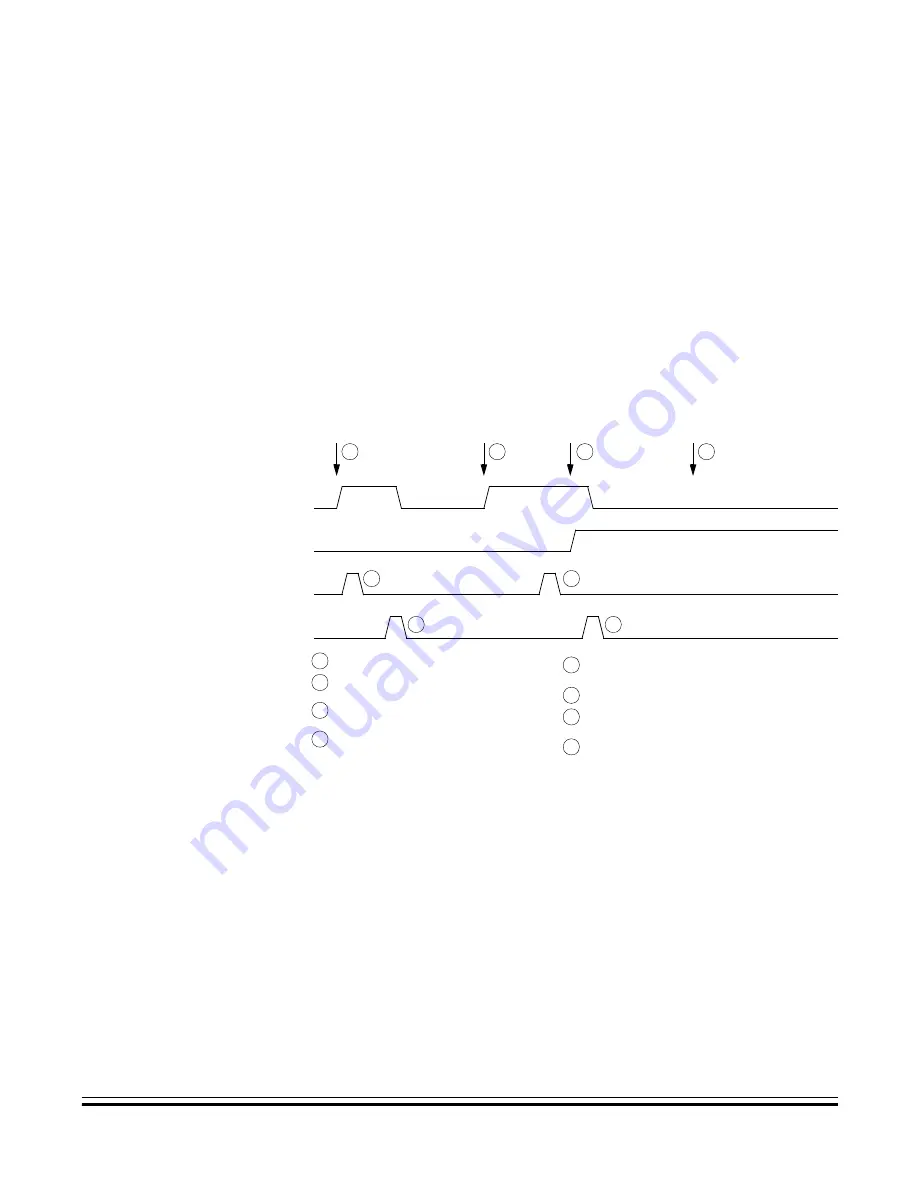

Figure 20-9

shows how it is possible to

miss an overflow. The first part of

Figure 20-9

shows how it is possible

to read the SPSCR and SPDR to clear the SPRF without problems.

However, as illustrated by the second transmission example, the OVRF

bit can be set in between the time that SPSCR and SPDR are read.

Figure 20-9. Missed Read of Overflow Condition

In this case, an overflow can be missed easily. Since no more SPRF

interrupts can be generated until this OVRF is serviced, it is not obvious

that bytes are being lost as more transmissions are completed. To

prevent this, either enable the OVRF interrupt or do another read of the

SPSCR following the read of the SPDR. This ensures that the OVRF

was not set before the SPRF was cleared and that future transmissions

can set the SPRF bit.

Figure 20-10

illustrates this process. Generally, to

avoid this second SPSCR read, enable the OVRF to the CPU by setting

the ERRIE bit.

READ

READ

OVRF

SPRF

BYTE 1

BYTE 2

BYTE 3

BYTE 4

BYTE 1 SETS SPRF BIT.

CPU READS SPSCR WITH SPRF BIT SET

CPU READS BYTE 1 IN SPDR,

BYTE 2 SETS SPRF BIT.

CPU READS SPSCR WITH SPRF BIT SET

BYTE 3 SETS OVRF BIT. BYTE 3 IS LOST.

CPU READS BYTE 2 IN SPDR, CLEARING SPRF BIT,

BYTE 4 FAILS TO SET SPRF BIT BECAUSE

1

1

2

3

4

5

6

7

8

2

3

4

5

6

7

8

CLEARING SPRF BIT.

BUT NOT OVRF BIT.

OVRF BIT IS NOT CLEARED. BYTE 4 IS LOST.

AND OVRF BIT CLEAR.

AND OVRF BIT CLEAR.

SPSCR

SPDR

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..