MC68HC08GP32

MC68HC908GP32

•

MC68HC08GP32

—

Rev. 6

Technical Data

MOTOROLA

MC68HC08GP32

401

A.5 Mask Option Registers

The two mask option registers at $001E and $001F (see

Figure A-3

and

Figure A-4

) are read-only registers. They are defined by mask options

(hard-wired connections) specified at the same time as the ROM code

submission.

On the MC68HC908GP32, these two registers are called configuration

registers (CONFIG2 and CONFIG1).

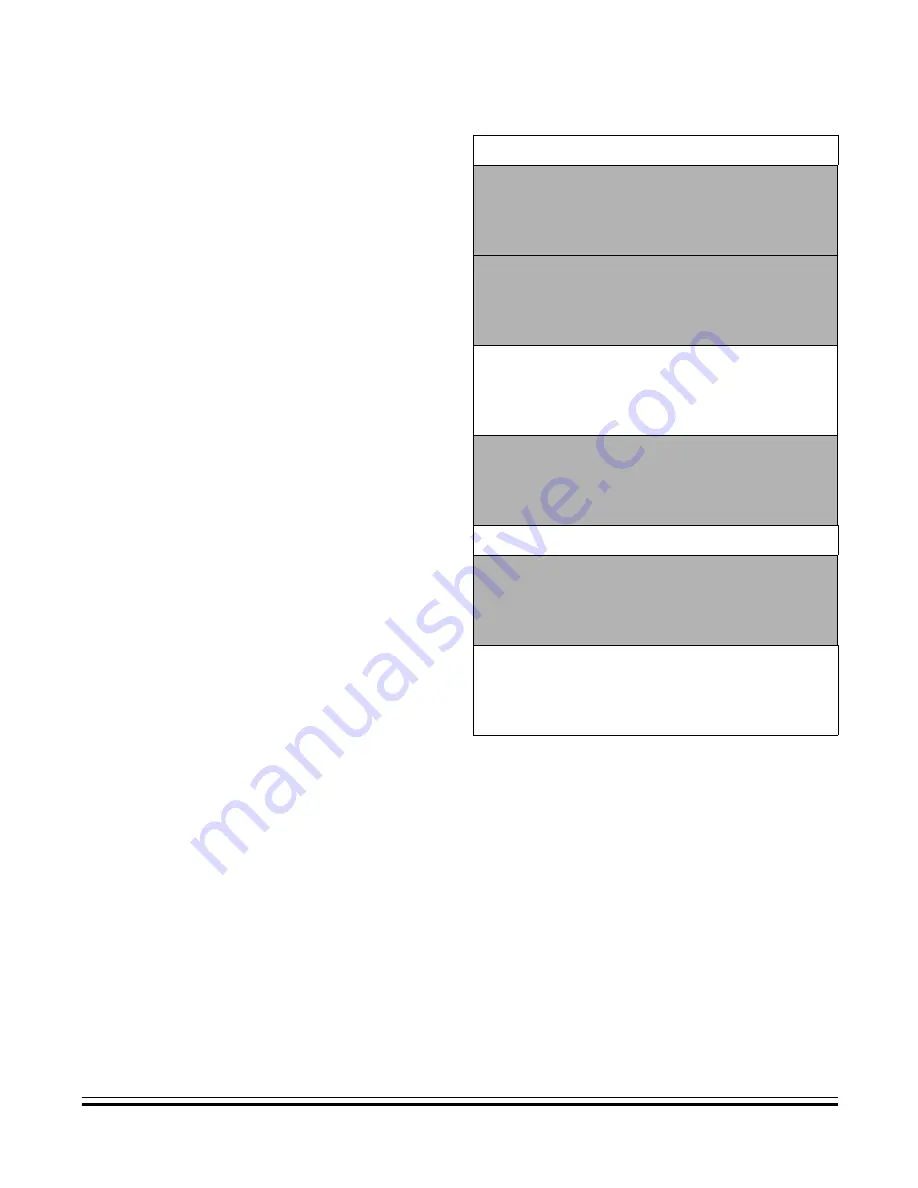

$FE0C

LVI Status Register (LVISR)

$FE0D

Unimplemented

3 Bytes

↓

$FE0F

$FE10

Unimplemented

16 Bytes

Reserved for Compatibility with Monitor Code

for A-Family Parts

↓

$FE1F

$FE20

Monitor ROM

307 Bytes

↓

$FF52

$FF53

Unimplemented

43 Bytes

↓

$FF7D

$FF7E

Reserved

$FF7F

Unimplemented

93 Bytes

↓

$FFDB

Note: $FFF6–$FFFD

reserved for

8 security bytes

$FFDC

ROM Vectors

36 Bytes

↓

$FFFF

Figure A-2. MC68HC08GP32 Memory Map (Continued)

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..