Memory Map

Input/Output (I/O) Section

MC68HC908GP32

•

MC68HC08GP32

—

Rev. 6

Technical Data

MOTOROLA

Memory Map

53

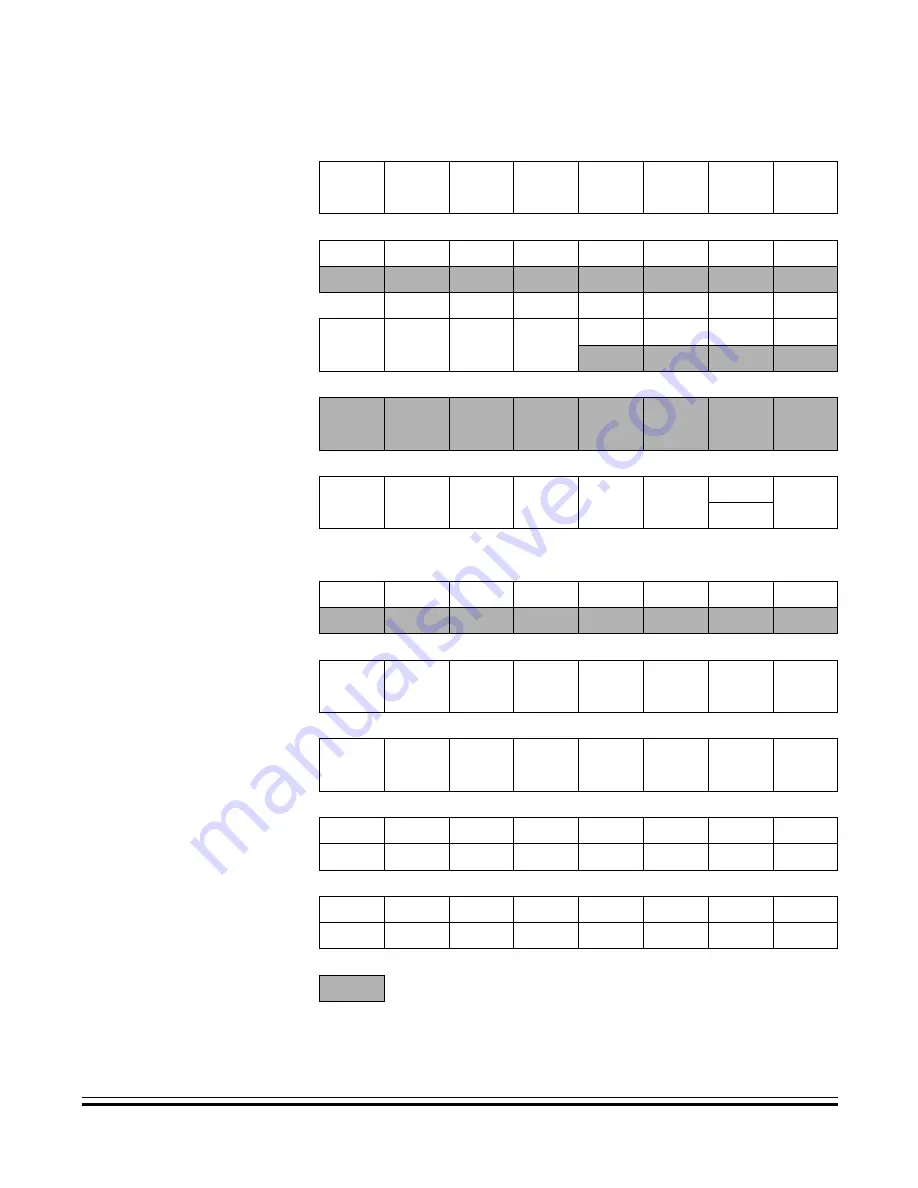

$003C

Analog-to-Digital Status

and Control Register

(ADSCR)

Read:

COCO

AIEN

ADCO

ADCH4

ADCH3

ADCH2

ADCH1

ADCH0

Write:

Reset:

0

0

0

1

1

1

1

1

$003D

Analog-to-Digital Data

Register

(ADR)

Read:

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

Write:

Reset:

0

0

0

0

0

0

0

0

$003E

Analog-to-Digital Clock

Register

(ADCLK)

Read:

ADIV2

ADIV1

ADIV0

ADICLK

0

0

0

0

Write:

Reset:

0

0

0

0

0

0

0

0

$003F

Unimplemented

Read:

Write:

Reset:

$FE00

SIM Break Status Register

(SBSR)

Read:

R

R

R

R

R

R

SBSW

R

Write:

Note

Reset:

0

Note: Writing a logic 0 clears SBSW.

$FE01

SIM Reset Status Register

(SRSR)

Read:

POR

PIN

COP

ILOP

ILAD

MODRST

LVI

0

Write:

POR:

1

0

0

0

0

0

0

0

$FE02

SIM Upper Byte Address

Register

(SUBAR)

Read:

R

R

R

R

R

R

R

R

Write:

Reset:

$FE03

SIM Break Flag Control

Register

(SBFCR)

Read:

BCFE

R

R

R

R

R

R

R

Write:

Reset:

0

$FE04

Interrupt Status Register 1

(INT1)

Read:

IF6

IF5

IF4

IF3

IF2

IF1

0

0

Write:

R

R

R

R

R

R

R

R

Reset:

0

0

0

0

0

0

0

0

$FE05

Interrupt Status Register 2

(INT2)

Read:

IF14

IF13

IF12

IF11

IF10

IF9

IF8

IF7

Write:

R

R

R

R

R

R

R

R

Reset:

0

0

0

0

0

0

0

0

Addr.

Register Name

Bit 7

6

5

4

3

2

1

Bit 0

= Unimplemented

R = Reserved

U = Unaffected

Figure 2-2. Control, Status, and Data Registers (Sheet 7 of 8)

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..