Resets and Interrupts

Technical Data

MC68HC908GP32

•

MC68HC08GP32

—

Rev. 6

72

Resets and Interrupts

MOTOROLA

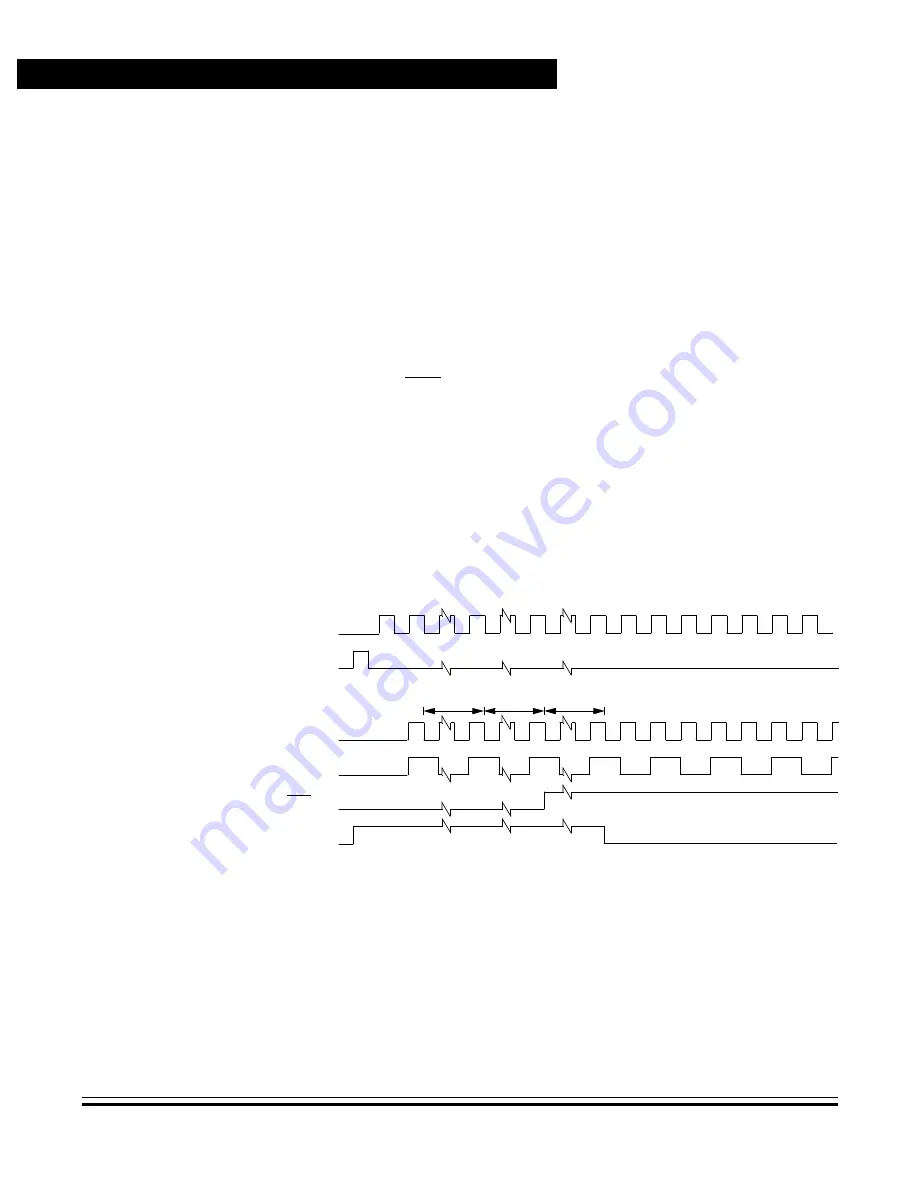

4.3.3.1 Power-On Reset

A power-on reset (POR) is an internal reset caused by a positive

transition on the V

DD

pin. V

DD

at the POR must go completely to 0 V to

reset the MCU. This distinguishes between a reset and a POR. The POR

is not a brown-out detector, low-voltage detector, or glitch detector.

A power-on reset:

•

Holds the clocks to the CPU and modules inactive for an oscillator

stabilization delay of 4096 CGMXCLK cycles

•

Drives the RST pin low during the oscillator stabilization delay

•

Releases the RST pin 32 CGMXCLK cycles after the oscillator

stabilization delay

•

Releases the CPU to begin the reset vector sequence 64

CGMXCLK cycles after the oscillator stabilization delay

•

Sets the POR and LP bits in the SIM reset status register and

clears all other bits in the register

Figure 4-2. Power-On Reset Recovery

PORRST

(1)

OSC1

CGMXCLK

CGMOUT

RST PIN

INTERNAL

4096

CYCLES

32

CYCLES

32

CYCLES

1. PORRST is an internally generated power-on reset pulse.

RESET

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..