Memory Maps

http://www.motorola.com/computer/literature

2-3

2

❏

The mapping of all resources as viewed by the processor (MPU bus

memory map)

❏

The mapping of onboard resources as viewed by PCI local bus

masters (PCI bus memory map)

❏

The mapping of onboard resources as viewed by the CompactPCI

bus.

The following sections provide a general description of the MCP750HA

memory organization from three points of view listed above. Detailed

memory maps can be found in the MCP750 Single Board Computer

Programmer's Reference Guide, listed in

Processor Memory Map

The processor memory map configuration is under the control of the

Raven bridge controller ASIC and the Falcon memory controller chip set.

The Raven and Falcon devices adjust system mapping to suit a given

application via programmable map decoder registers. At system power-up

or reset, a default processor memory map takes over.

Default Processor Memory Map

The default processor memory map that is valid at power-up or reset

remains in effect until reprogrammed for specific applications.

defines the entire default memory map ($00000000 to $FFFFFFFF).

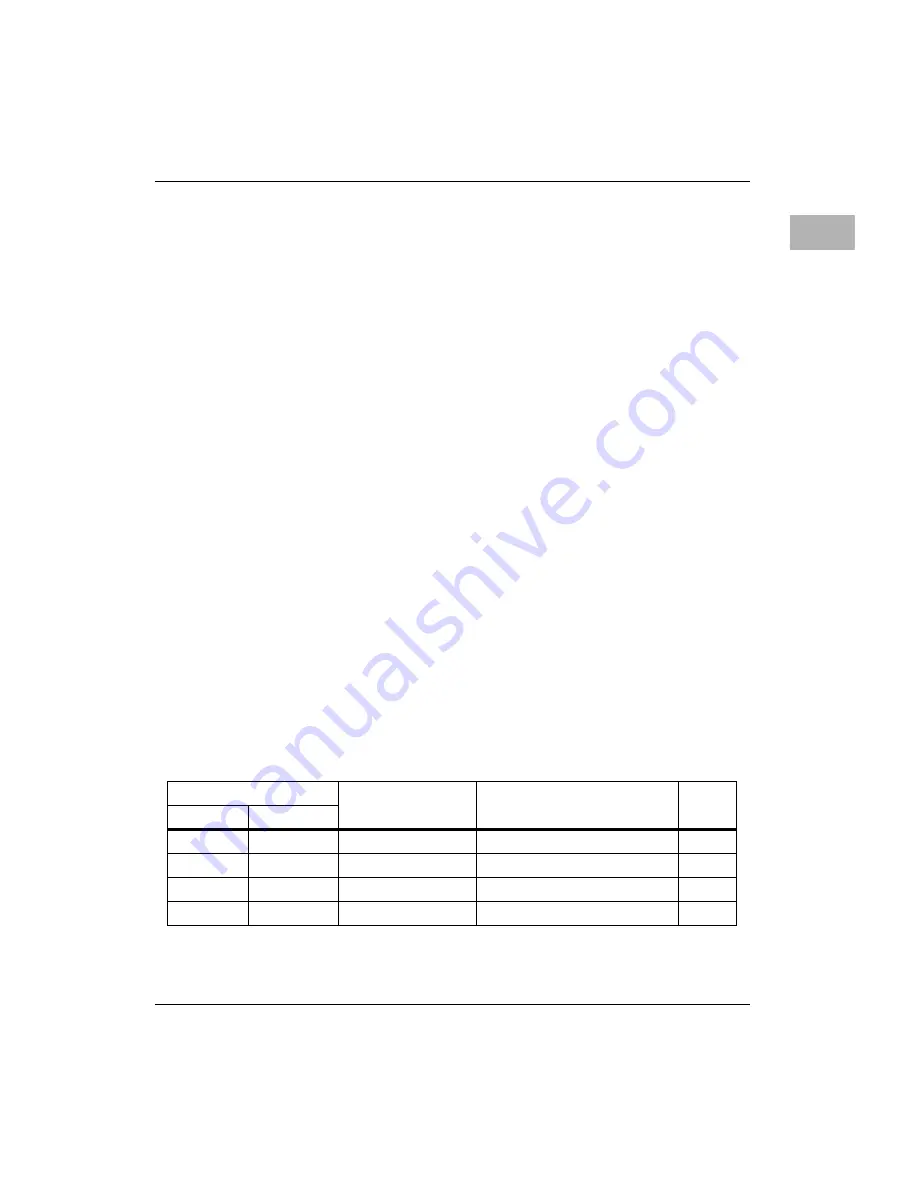

Table 2-1. Processor Default View of the Memory Map

Processor Address

Size

Definition

Notes

Start

End

00000000

7FFFFFFF

2GB

Not Mapped

80000000

8001FFFF

128KB

PCI/ISA I/O Space

1

80020000

FEF7FFFF

2GB-16MB-640KB

Not Mapped

FEF80000

FEF8FFFF

64KB

Falcon Registers

Summary of Contents for MCP750HA Series

Page 161: ......