Block Diagram

http://www.motorola.com/computer/literature

3-17

3

modified within the Z85230 according to the interrupt source. Interrupt

request levels are programmed via the PBC. All modem control lines from

the ESCC are multiplexed/de-multiplexed through J3 by the P2MX

function due to I/O pin limitations. Refer to the Z85230 data sheet and to

the MCP750 Single Board Computer Programmer's Reference Guide for

additional information.

Z8536 CIO Device

The Z8536 CIO device complements the Z85230 ESCC by supplying

modem control lines not provided by the Z85230 ESCC. In addition, the

Z8536 CIO device has three independent 16-bit counters/ timers. The

Z85230 receives a 5 MHz clock input.

MCP750HA Board Identifier

The MCP750HA CPU board is uniquely identified by the following

registers:

❏

The CPU Configuration Register is an 8-bit register located at

ISA I/O address x0800. The CPUType field will return Eh for the

MCP750HA.

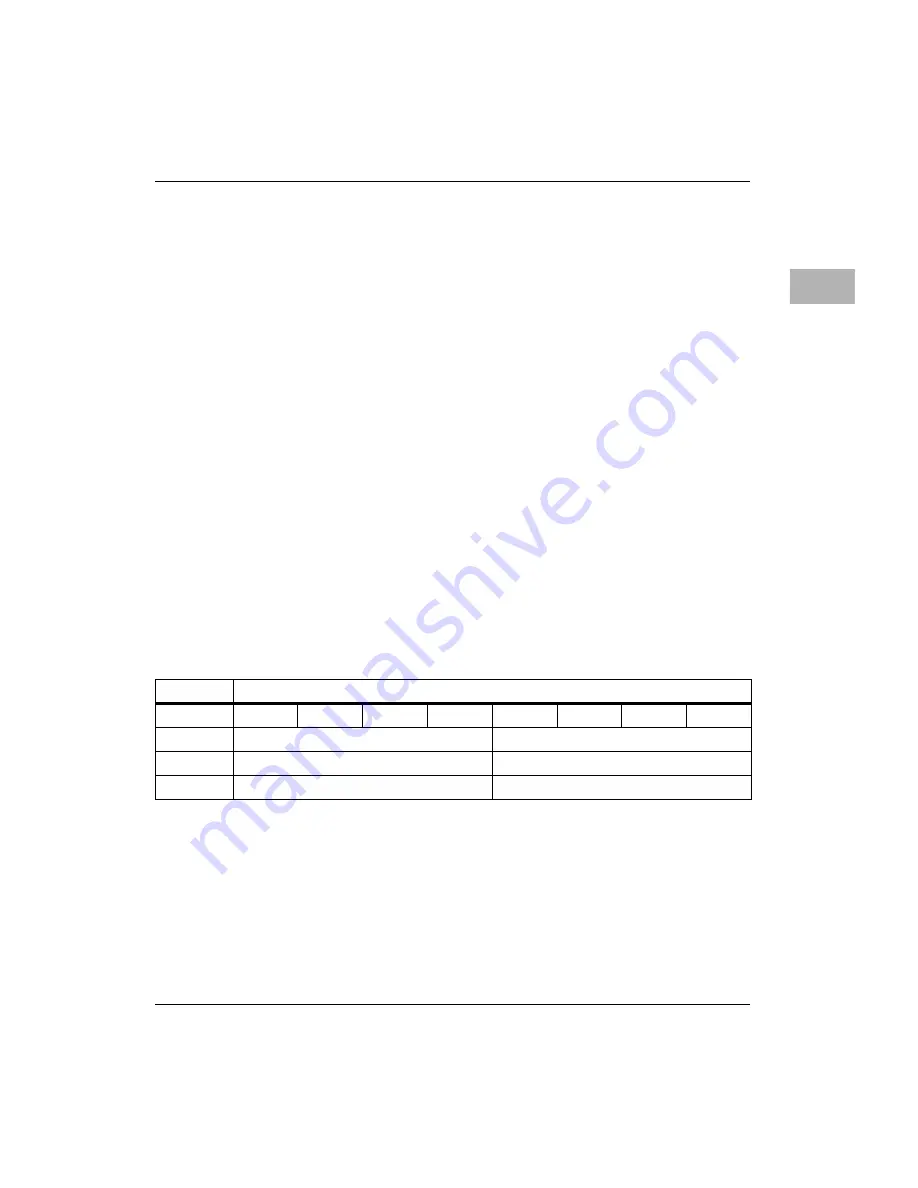

Table 3-3. Old CPU Configuration Register

REG

Old CPU Configuration Register - $FE000800

BIT

SD7

SD6

SD5

SD4

SD3

SD2

SD1

SD0

FIELD

CPUTYPE

OPER

R

R

RESET

$E

$F

Summary of Contents for MCP750HA Series

Page 161: ......