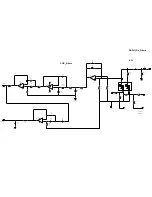

RESET

ABORT

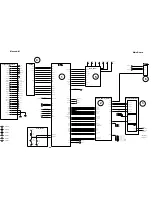

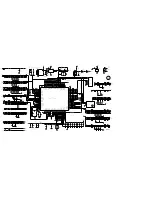

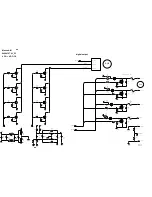

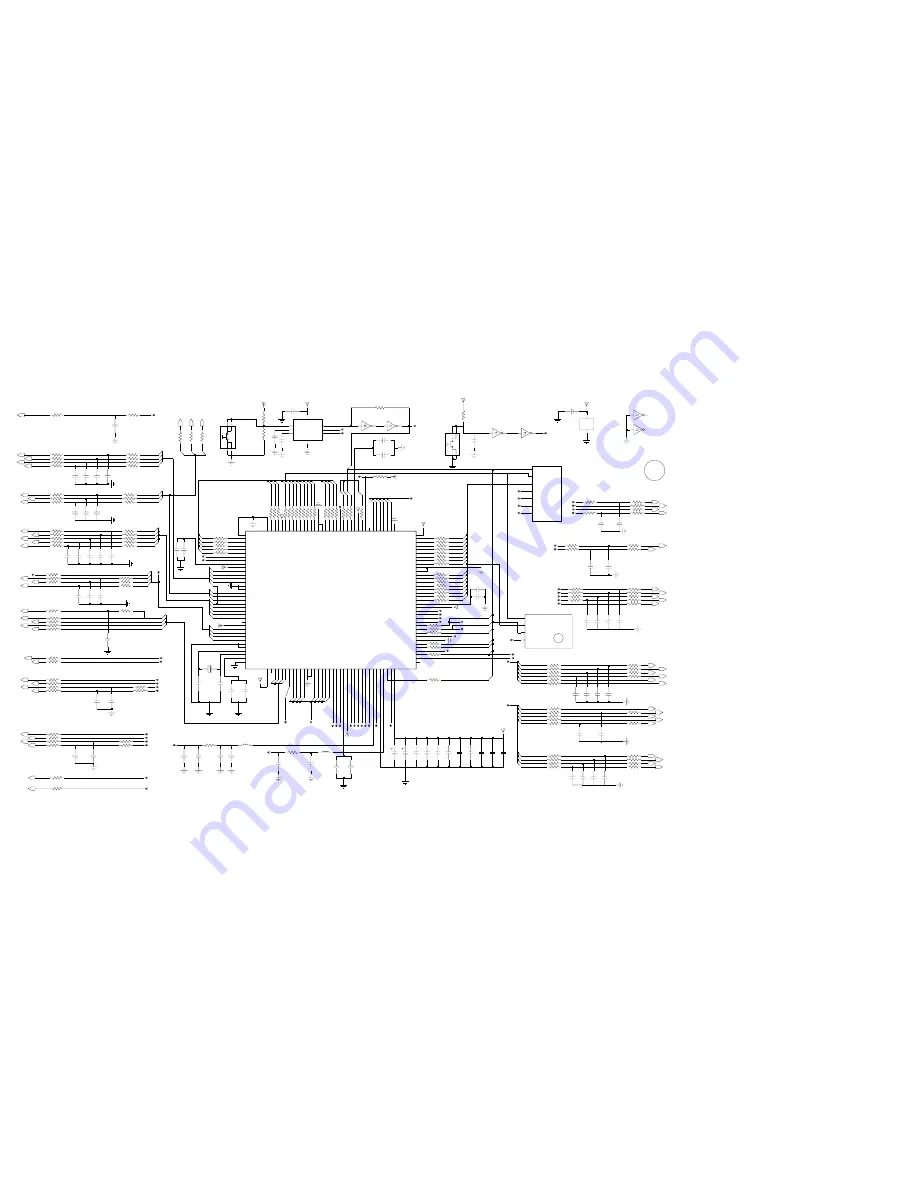

MC68VZ328

PB2/CSC0

PB5/CSD1

reset every 880mS

Reset period 1.2S

PU defines 16b BUS

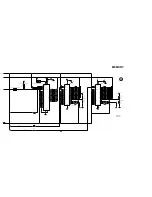

pwm_to_dc converters

1.1

1.2

1

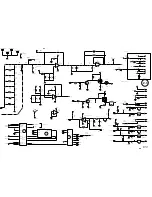

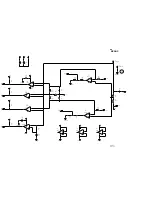

S3 and S2 are used only for debuging

73D02962C89-O

SHEET 2 OF 23

N.C.

N.C.

EMULATOUR(1:4)

PG0_DTACK

PG1_A0

SGND

SGND

SGND

SGND

SGND

MEMORY

PG0

D(0:15)

CONTROL(1:11)

A(1:21)

1.K

PK3_UDS

PK3

PK4_LD4

PK4

PB3_CSC1

R1349

R1350

PK5-LD5

R990

300

R994

1.K

300

R992

R993

1.K

PWM1_FIL

PB7_PWM1

PWM2_FIL

PK0_SPIRDY_PWM2

1.K

B6_TOUT_TIN

1.K

PE4_RXD1

PE5_TXD1

PE6_RTS1

PE7_CTS1

PG3_HIZ

PG4_EMUCS

PJ3_SS

PJ2_SPICLK1

PJ0_MISO

PJ1_MOSI

PC6_LCLK

PC5_LLP

PC4_LFRM

PC2_LD2

PC1_LD1

PC0_LD0

PK7_LD7

PK6_LD6

PM2_

PM0_

INTERUPTS(1:9)

PM1_

PF0_CONTRAST

PG1_A0

PORT_M(1:6)

PM5_

PM4_

PM3_

IRQ1

INT3

INT2

INT1

INT0

PM5

PM4

PM3

PM2

PM1

PM0

PF0

PC7

PC6

PC5

PC4

PC2

PC1

PC0

PK5

PK6

PK7

PG1

PK3

PB3

C401

R996

1.K

R1346

R991

1.K

1.K

R1347

1.K

100p

C592

R1348

R997

AD(21)

PWM2_FIL

PWM1_FIL

SPITXD2

SPIRXD2

SPICLK2

PJ3_ex

IRQ5_

IRQ6_

IRQ3_

IRQ2

IRQ1_

INT3_

INT2_

INT1_

INT0_

PB4_

PC3

PB6

~EMUIRQ

PF5_

PF5

PF6_

PF6

PB5_

PB5

PB4_

PB4

PB2_

PB2

PB3

PF7

PK2_LDS

AD(20)

SGND

1.K

R1436

R1106

100.n

C595

3.9n

L41

100p

SGND

SGND

C593

L43

3.9n

1.K

R1434

R865

1K

3

47

R1441

1

2

R1440

47

SGND

47

R1439

C594

100n

330.n

C586

1.K

R1354

R1355

1.K

R1353

1.K

1.K

R1352

R1351

1.K

1.K

R1345

1.K

1.K

R1344

1.K

R1342

R1343

1.K

R1340

R1341

1.K

1.K

C579

20p

R1359

120.

R1358

20p

C578

120.

120.

120.

R1357

SGND

SGND

R1356

R1194

0

MC74HC14A

U46

9

8

SGND

U46

MC74HC14A

11

10

47

R1319

R1318

47

47

R1317

47

R1315

R1316

47

R1314

47

47

R1313

47

R1311

R1310

47

47

R1309

SGND

R1308

47

100.p

C536

100.p

C535

C534

100.p

1.K

R1223

R1224

1.K

SGND

R1222

1.K

C532

100.p

1.K

R1219

1.K

R1218

C530

SGND

100.p

C529

100.p

C528

100.p

100.p

C527

R1217

1.K

R1216

1.K

1.K

R1214

1.K

R1215

100.p

SGND

C526

100.p

C525

100.p

C524

C523

100.p

1.K

R1212

R1213

1.K

R1210

R1211

1.K

1.K

100

1.K

R1207

R1208

100.p

C521

SGND

C522

C519

100.p

SGND

100.p

100.p

C518

1.K

R1206

R1205

300

C517

SGND

100.p

100.p

C516

R1204

300

1.K

R1203

100.p

SGND

C514

C515

1.K

R1202

100.p

R1201

1.K

C390

100.p

1K

R876

1K

R879

1K

R860

R1198

R1199

1K

1K

R1197

1K

120

R1306

R1305

120

120

R878

R877

120

R875

120

R874

120

1K

R1196

R1195

1K

120

R1304

120

120

R1303

C32

R1302

1.u

100.K

R338

C296

100.p

R1187

SGND

C513

51.K

U46

13

12

1.u

5

6

MC74HC14A

21

MC74HC14A

U46

R1150

47

1.K

R1031

R1030

1.K

1.K

R1029

MC74HC14A

3

4

MC74HC14A

U46

1

2

U46

V_KeepAlive

V_KeepAlive

V_KeepAlive

V_KeepAlive

V_KeepAlive

V_KeepAlive

V_KeepAlive

V_KeepAlive

SGND

SGND

SGND

V_KeepAlive

V_KeepAlive

V_KeepAlive

V_KeepAlive

V_KeepAlive

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

SGND

R1149

20

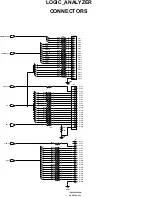

ANALYZER

A(1:21)

CLKO_PF2

CONTROL(1:11)

D(0:15)

47

R1028

1.K

R1021

1.K

100.K

R959

R1020

1.K

100

R1013

R1010

1.K

120.

R1109

120.

R1108

R1107

120.

1.K

100.p

R882

1K

R989

1.K

1.K

R988

R987

1.K

1.K

R986

R985

1.K

R984

1.K

1.K

R983

1.K

R982

1.K

R981

R980

1.K

6

7

8

9

5

6

1

2

3

4

5

1

2

3

4

4

B2

SWITCH

S2

A1

1

2

A2

3

B1

S3

1

A1

A2

2

B1

3

B2

4

7

GND

14

VCC

8

11

SWITCH

5

U46

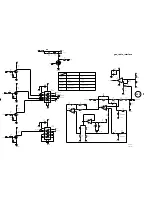

PWR_GND

100.K

R857

C351

100n

C360

330.n

R677

1.M

R892

1.3M

4

100n

VCC

8

WDI

6

WDS

5

C352

MAX6303ESA

U53

GND

2

RESET

7

RESET_IN

1

SRT

3

SWT

4

100.p

C386

C385

100.p

100.p

C384

R864

1K

1K

R863

1K

C383

100.p

R862

C382

20p

C381

20p

100.p

C380

100.p

C379

100.p

C490

10.n

C479

20p

C398

C397

20p

20p

C396

R873

120

100.p

C395

C394

20p

C393

20p

R1301

R870

120

1K

C392

100.p

R869

1K

47

R1122

47

R1120

R1121

47

R1119

47

47

R1118

R1117

47

47

R1116

47

47

R1114

R1115

R1148

47

47

R1147

R1146

47

47

R1145

47

47

R1143

R1144

R1142

47

R1141

47

47

R1140

R1139

47

47

R1138

47

R1136

R1137

47

R1135

47

47

R1134

47

R1133

R1132

47

47

R1131

R1130

47

47

47

R1129

R1127

R1128

47

47

R1126

47

47

R1125

R1124

3

4

V_KeepAlive

47

R1123

5

1

2

3

4

1

2

2

3

1

2

3

4

1

2

3

4

1

C489

100.p

C464

220.n

100.p

C488

10.n

C478

C487

100.p

9

10

C477

10.n

C486

5

6

7

100.p

6

10.n

C476

1

2

3

4

5

9

C353

100n

3

4

5

6

7

8

4

1

2

3

4

1

2

3

4

5

1

2

3

1 2

3

4

1

2

12

13

14

15

1

2

3

6

7

8

9

10

11

0

1

2

3

4

5

4

3

2

1

17

18

19

10

9

8

7

6

5

1

16

15

14

13

12

11

VCC7

119

VCC8

140

VCC9

34

XTAL

2

3

4

TP5

122

UWE_UB

10

VCC1

26

VCC2

37

VCC3

59

VCC4

72

VCC5

88

VCC6

108

PM4_SDA10

115

PM5_DMOE

118

RESET

99

TP0

130

TP1

15

TP2

31

TP3

36

TP4

48

PK5_LD5

86

PK6_LD6

87

PK7_LD7

69

PKO_SPIRDY_PWM02

110

PM0_SDCLK

111

PM1_SDCE

112

PM2_DQMH

113

PM3_DQML

114

PJ4_RXD2

12

PJ5_TXD2

13

PJ6_RTS2

14

PJ7_CTS2

70

PK1_RW

82

PK2_LDS

83

PK3_UDS

84

PK4_LD4

85

PG2_EMUIRQ

28

PG3_HIZ_PD

29

PG4_EMUCS

30

PG5_EMUBRK

42

PJ0_MOSI

41

PJ1_MISO

40

PJ2_SPICLK1

39

PJ3_SS

11

PF2_CLKO

5

PF3_A20

6

PF4_A21

7

PF5_A22

8

PF6_A23

80

PF7_CSA1

117

PG0_BUSW_DTACK

124

PG1_A0

27

PE2_SPICLK2

20

PE3_DWE_UCLK

21

PE4_RXD1

22

PE5_TXD1

23

PE6_RTS1

24

PE7_CTS1

55

PF0_CONTRAST

PF1_IRQ5

44

43

PD2_INT2

51

PD3_INT3

50

PD4_IRQ1

47

PD5_IRQ2

46

PD6_IRQ3

45

PD7_IRQ6

17

PE0_SPITXD

18

PE1_SPIRXD

19

PC2_LD2

62

PC3_LD3

PC4_LFRM

61

60

PC5_LLP

57

PC6_LCLK

56

PC7_LACD

54

PD0_INT0

53

PD1_INT1

52

PB2_CSC0_RAS0

75

PB3_CSC1_RAS1

74

PB4_CSD0_CAS0

71

PB5_CSD1_CAS1

67

PB6_TOUT_TIN

66

PB7_PWMO1

65

PC0_LD0

64

PC1_LD1

63

MA8_A9

136

MA9_A10

25

NC1

38

NC2

73

NC3

116

NC4

78

PB0_CSB0

77

PB1_CSB1_SDWE

76

MA15_A16

126

MA1_A2

127

MA2_A3

128

MA3_A4

131

MA4_A5

132

MA5_A6

133

MA6_A7

134

MA7_A8

135

LVCC5

123

LWE_LB

125

MA0_A1

137

MA10_A11

138

MA11_A12

139

MA12_A13

141

MA13_A14

142

MA14_A15

143

GND6

98

GND7

109

GND8

129

GND9

9

LVCC1

35

LVCC2

58

LVCC3

89

LVCC4

120

EN_OE

33

EXTAL

1

GND1

144

GND10

16

GND2

32

GND3

49

GND4

68

GND5

79

D2_PA2

104

D3_PA3

103

D4_PA4

102

D5_PA5

101

D6_PA6

100

D7_PA7

97

D8

96

D9

121

D0_PA0

95

D10

94

D11

93

D12

92

D13

91

D14

90

D15

106

D1_PA1

105

2

A17

3

A18

4

A19

81

CSA0

107

MC68VZ328CPV33V

U52

C350

100n

C348

C349

100n

100n

100n

C347

10u

C336

100n

C346

10u

C335

100n

C345

C344

C343

100n

100n

20p

C376

Y2

32.768K

C375

20p

PG5_EMUBRK

RESET~

~EMUIRQ

PF2

PG0_DTACK

PG1_A0

EMULATOUR(1:4)

PC7_LACD

PC3_LD3

PB2_

PG0_DTACK

PJ4_RXD2

PJ5_TXD2

PJ6_RTS2

PJ7_CTS2

PE0_SPITXD

PE1_SPIRXD

PE2_SPICLK2

PE3_UCLK

PB6

PK0

PB5_

PK2_LDS

C_RTS2

C_UCLK

C_RXD1

C_TXD1

C_RTS1

C_CTS1

C_RXD2

C_TXD2

C_CTS2

C_SPITXD

C_SPIRXD

C_SPICLK2

~HIZ

~EMUCS

~EMUBRK

C_SS

C_SS

PJ2

PJ0

PJ1

IRQ5

IRQ6

IRQ3

EMUBRK_IRQ2

AD(16)

AD(17)

AD(18)

AD(19)

PF5_

PF6_

CPU_UART_2(1:5)

EMULATOUR(1:4)

EMULATOUR(1:4)

AD(1)

CPU_SPI_1(1:4)

CPU_SPI_2(1:3)

CPU_SPI_2(1:3)

CPU_UART_1(1:5)

INTERUPTS(1:9)

PORT_M(1:6)

PF0

PC7

PC6

PC5

PC4

PC3

PC2

PC1

PC0

PB7

D(15)

AD(2)

AD(3)

AD(4)

AD(5)

AD(6)

AD(7)

AD(8)

AD(9)

AD(10)

AD(11)

AD(12)

AD(13)

AD(14)

AD(15)

D(0)

D(1)

D(2)

D(3)

D(4)

D(5)

D(6)

D(7)

D(8)

D(9)

D(10)

D(11)

D(12)

D(13)

D(14)

A(1:21)

A(1:21)

A(1:21)

D(0:15)

D(0:15)

CONTROL(1:11)

CONTROL(1:11)

CONTROL(1:11)

CONTROL(1:11)

CSA0

PF2

PF7

PG0_DTACK

PG1

PK4

PK5

PK6

PK7