3-18

MPC8240 Integrated Processor User’s Manual

Embedded Utilities Memory Block (EUMB)

The lower-order address bits of the base address field of OTWR that are within the range

specified by the window size are ignored and the MPC8240 ignores the outgoing

lower-order address bits (within the range specified by the window size). However, for

future compatibility, it is recommended that the base address be programmed to be

naturally aligned to the window size.

3.4 Embedded Utilities Memory Block (EUMB)

The MPC8240 contains several embedded features that require control and status registers.

These registers are accessible during normal operation. The features include the DMA

controller, message unit, EPIC, I

2

C, ATU, and memory data path diagnostic logic

(including watchpoint facility). These registers in some cases are accessible by both the

processor core and the PCI bus. The collection of these units is called the embedded

utilities. These registers comprise the runtime registers and a block of local memory and

PCI memory space is allocated to them.

The embedded utilities memory block (EUMB) is relocatable both in PCI memory space

(for PCI access) and local memory space (for processor access). The local memory map

location of this register block is controlled by the embedded utilities memory block base

address register (EUMBBAR). In the processor’s local memory map, the registers that

comprise the EUMB (specified by the EUMBBAR) are restricted to locations

0x8000_0000 to 0xFDFF_FFFF; see Section 3.4, “Embedded Utilities Memory Block

(EUMB).” The PCI bus memory map location for this block is controlled by the peripheral

control and status registers base address register (PCSRBAR). In the PCI memory space,

the registers of the EUMB (specified by PCSRBAR) may reside in any unused portion of

the PCI memory space; see Section 4.2.7, “PCI Base Address Registers—LMBAR and

PCSRBAR.”

Note that the EUMB should not reside inside either the outbound memory window or the

outbound translation window. Operation is not guaranteed if the two are overlapping. Note

that the processor must not run transactions to the PCI memory space allocated for the

EUMB by the PCSRBAR.

All registers in the EUMB are accessible with 32-bit accesses only. Transactions of sizes

other than 32-bit are considered a programming error, and operation is not guaranteed if

they are used. Additionally, accesses to the EUMB must be strictly ordered. Therefore, the

EUMB should be marked caching-inhibited and guarded using the WIMG memory/cache

access attributes in the processor’s BAT or page table entries. Note that the eieio instruction

has no effect on the MPC603e and MPC750 families of processors.

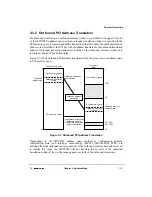

3.4.1 Processor Core Control and Status Registers

The location of the memory mapped registers of the EUMB that are accessible by the

processor for the message unit, DMA controller, ATU, I

2

C controller, EPIC unit, and

memory data path diagnostic logic are shown in Figure 3-12.

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...