Chapter 4. Configuration Registers

4-5

Configuration Register Access

Example: Map A configuration sequence, 4-byte data write to register at address offset

0xA8, using byte-swapped values in the processor registers

Initial values:r0 contains 0xA800_0080

r1 contains 0x8000_0CF8

r2 contains 0xDDCC_BBAA

Register at 0xA8 contains 0xFFFF_FFFF (AB to A8)

Code sequence:

stw

r0,0(r1)

sync

stw

r2,4(r1)

sync

Results:Address 0x8000_0CF8 contains 0x8000_00A8 (MSB to LSB)

Register at 0xA8 contains 0xAABB_CCDD (AB to A8)

4.1.3 Configuration Register Summary

The following sections summarize the addresses and attributes of the configuration

registers accessible by both the processor and the PCI interface.

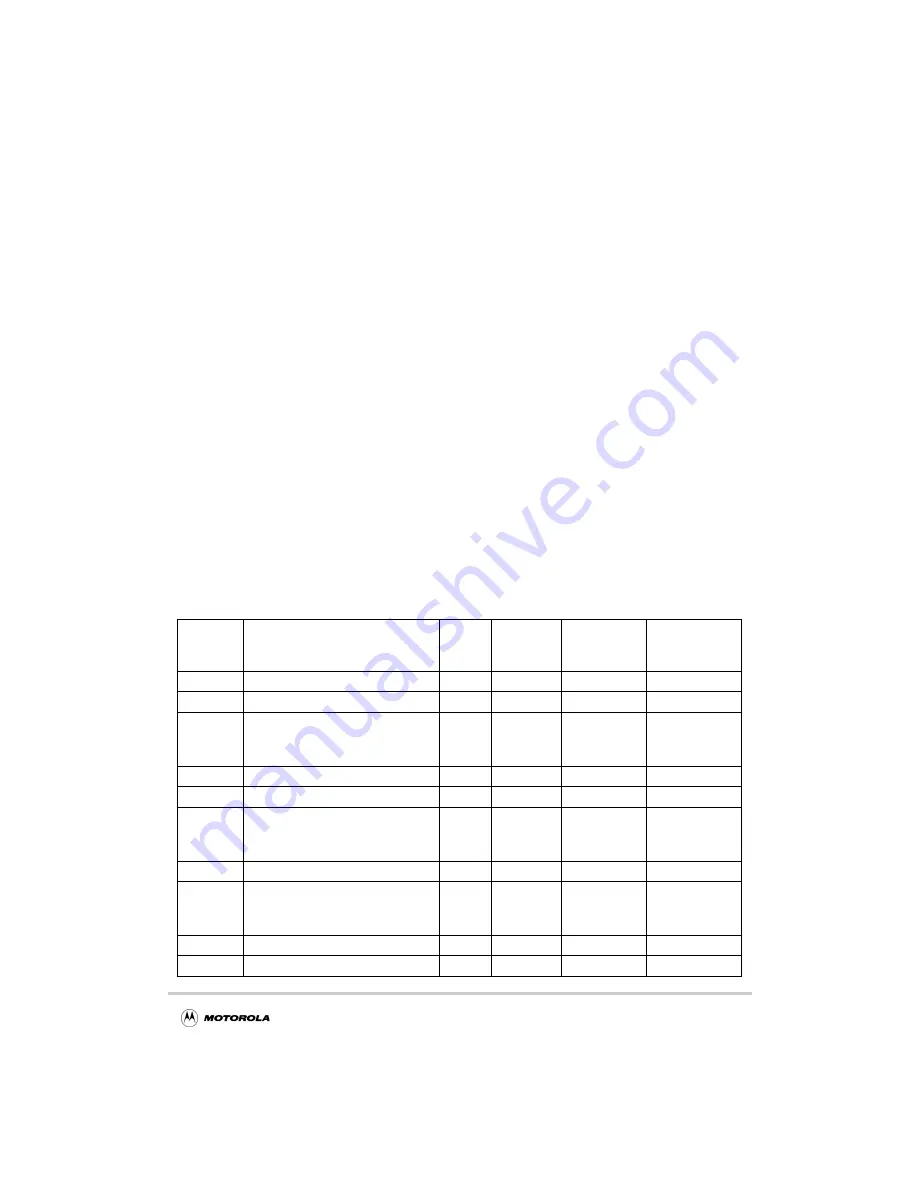

4.1.3.1 Processor-Accessible Configuration Registers

Table 4-2 describes the configuration registers that are accessible by the processor core. Not

all registers are shown in this document. Note that any configuration addresses not defined

in Table 4-2 are reserved.

Table 4-2. MPC8240 Configuration Registers Accessible

from the Processor Core

Address

Offset

Register

Size

Program

Access

Size (Bytes)

Access

Reset Value

0x00

Vendor ID = 0x1057 (not shown)

2 bytes

2

Read

0x1057

0x02

Device ID = 0x0003 (not shown)

2 bytes

2

Read

0x0003

0x04

PCI command register

2 bytes

2

Read/Write

mode-dependent

0x0004 host

0x0000 agent

0x06

PCI status register

2 bytes

2

Read/Bit Reset

0x00A0

0x08

Revision ID (not shown)

1 byte

1

Read

0xnn

0x09

Standard programming interface

1 byte

1

Read

mode-dependent

0x00 host

0x01 agent

0x0A

Subclass code (not shown)

1 byte

1

Read

0x00

0x0B

Class code

1 byte

1

Read

mode-dependent

0x06 host

0x0E agent

0x0C

Cache line size

1 byte

1

Read/Write

0x00

0x0D

Latency timer

1 byte

1

Read/Write

0x00

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...