Chapter 4. Configuration Registers

4-9

Configuration Register Access

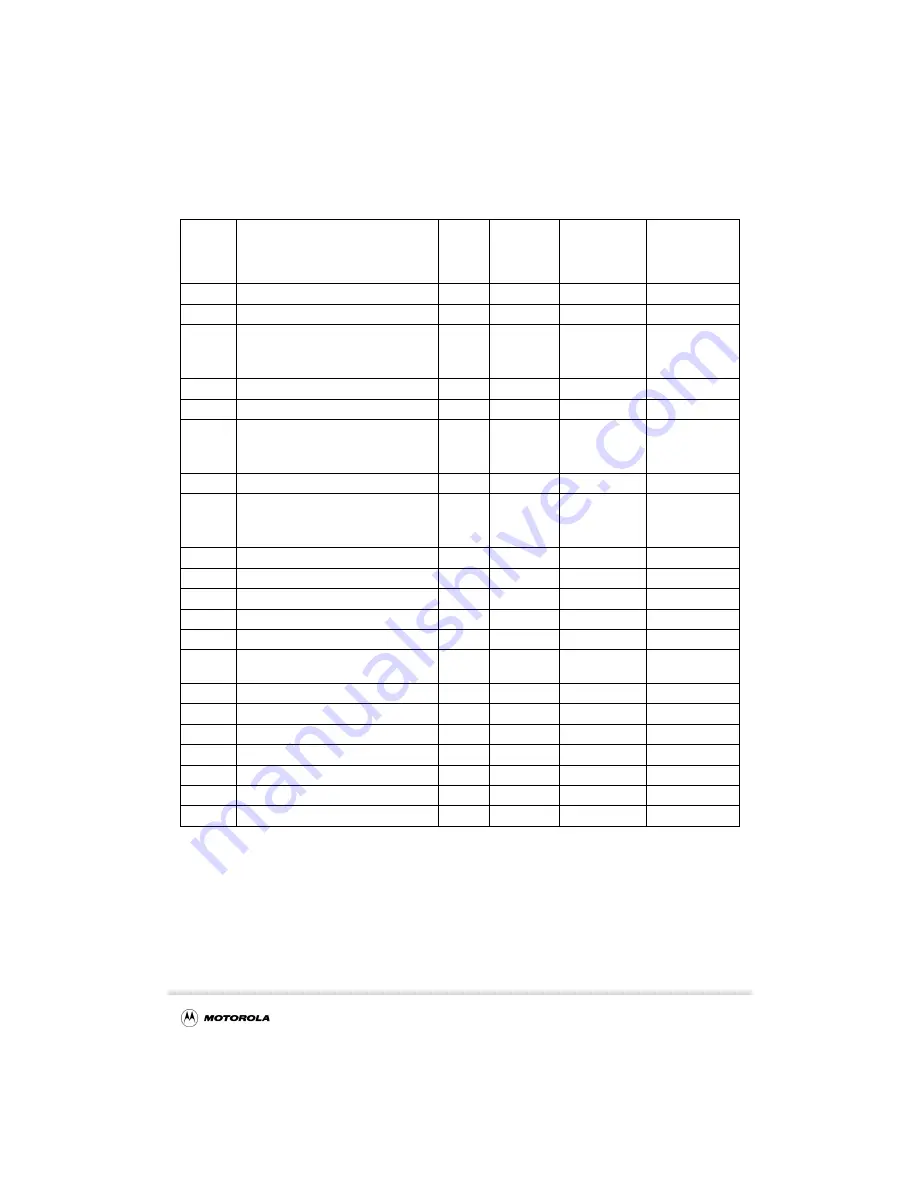

Table 4-3. MPC8240 Configuration Registers Accessible from the PCI Bus

Address

Offset

Register

Size

Program

Access

Size

(Bytes)

Access

Reset Value

0x00

Vendor ID = 0x1057

2-bytes

2

Read

0x1057

0x02

Device ID = 0x0003

2-bytes

2

Read

0x0003

0x04

PCI command register

2-bytes

2

Read/Write

mode-dependent

0x0004 host

0x0000 agent

0x06

PCI status register

2-bytes

2

Read/Bit-Reset

0x00A0

0x08

Revision ID

1-byte

1

Read

0xnn

0x09

Standard programming interface

1-byte

1

Read

mode-dependent

0x00 host

0x01 agent

0x0A

Subclass code

1-byte

1

Read

0x00

0x0B

Class code

1-byte

1

Read

mode-dependent

0x06 host

0x0E agent

0x0C

Cache line size

1-byte

1

Read/Write

0x00

0x0D

Latency timer

1-byte

1

Read/Write

0x00

0x0E

Header type

1-byte

1

Read

0x00

0x0F

BIST control

1-byte

1

Read

0x00

0x10

Local memory base address register

4-bytes

4

Read/Write

0x0000_0008

0x14

Peripheral control and status register

base address register

4-bytes

4

Read/Write

0x0000_0000

0x30

Expansion ROM base address

4 bytes

4

Read

0x0000_0000

0x3C

Interrupt line

1-byte

1

Read/Write

0x00

0x3D

Interrupt pin

1-byte

1

Read

0x01

0x3E

MIN GNT

1-byte

1

Read

0x00

0x3F

MAX LAT

1-byte

1

Read

0x00

0x46

PCI arbiter control register

2-bytes

2

Read/Write

0x0000

Others

Reserved

—

—

—

—

Note: Reset values marked mode-dependent are defined by whether the MPC8240 is operating in host or agent

mode.

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...