4-12

MPC8240 Integrated Processor User’s Manual

PCI Interface Configuration Registers

The 2-byte PCI status register, shown in Figure 4-4, is used to record status information for

PCI bus-related events. The definition of each bit is given in Table 4-6. Only 2-byte

accesses to address offset 0x06 are allowed.

4.2.2 PCI Status Register—Offset 0x06

The 2-byte PCI status register, shown in Figure 4-4, is used to record status information for

PCI bus-related events. The definition of each bit is given in Table 4-6. Only 2-byte

accesses to address offset 0x06 are allowed.

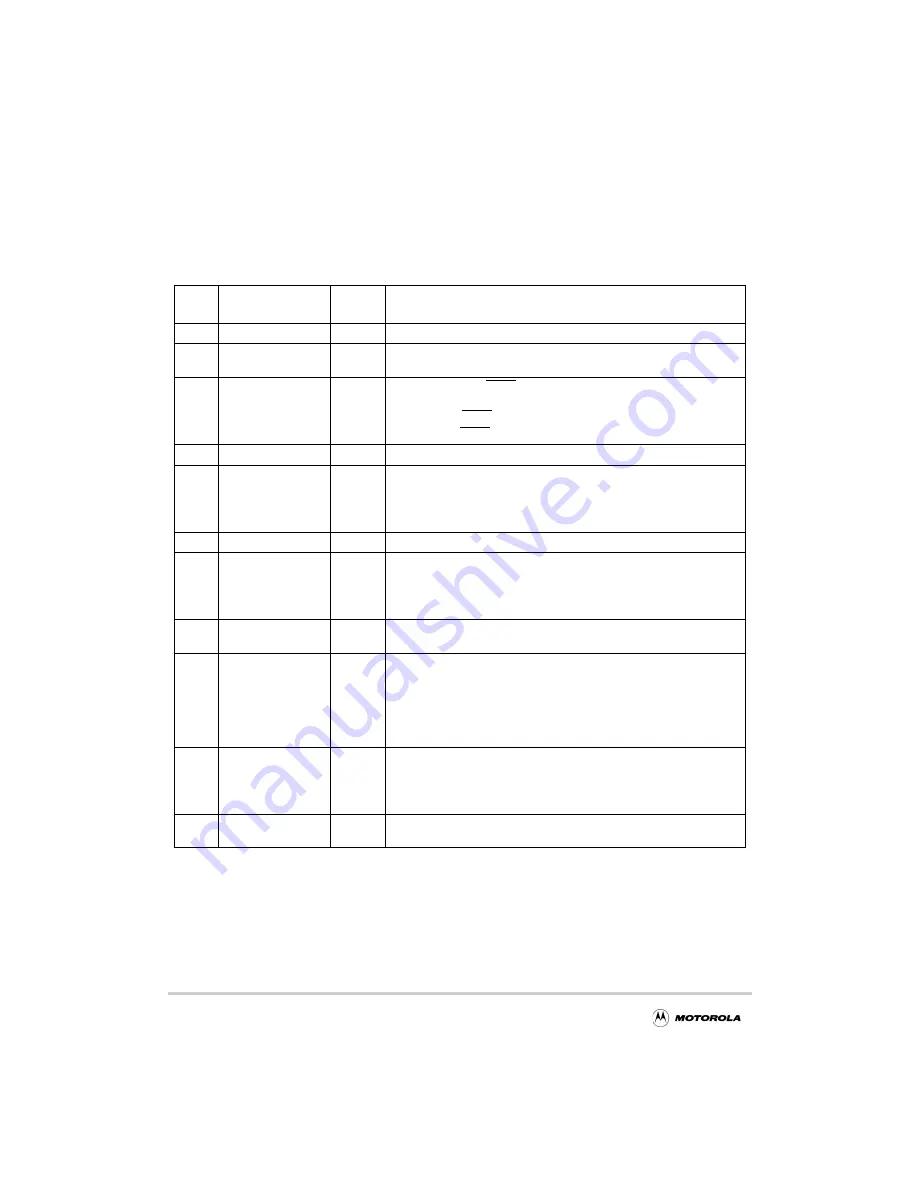

Table 4-5. Bit Settings for PCI Command Register—0x04

Bits

Name

Reset

Value

Description

15–10

—

All 0s

These bits are reserved.

9

Fast back-to-back

0

This bit is hardwired to 0, indicating that the MPC8240 does not run fast

back-to-back transactions.

8

SERR

0

This bit controls the SERR driver of the MPC8240. This bit (and bit 6)

must be set to report address parity errors.

0 Disables the SERR driver

1 Enables the SERR driver

7

—

0

This bit is reserved.

6

Parity error response

0

This bit controls whether the MPC8240 responds to parity errors.

0 Parity errors are ignored and normal operation continues.

1 Action is taken on a parity error. See Chapter 13, “Error Handling,” for

more information.

5

—

0

This bit is reserved.

4

Memory-write-and-

invalidate

0

This bit enables generation of the memory-write-and-invalidate command

by the MPC8240 as a master.

0 Memory-write command used by MPC8240.

1 Memory-write-and-invalidate command used by MPC8240.

3

Special cycles

0

This bit is hardwired to 0, indicating that the MPC8240 (as a target)

ignores all special-cycle commands.

2

Bus master

1 (host)

0 (agent)

This bit controls whether the MPC8240 can act as a master on the PCI

bus. Note that if this bit is cleared, processor-to-PCI writes cause the data

to be held until it is enabled. Processor to PCI reads with master disabled

cause a machine check exception (if enabled).

0 Disables the ability to generate PCI accesses

1 Enables the MPC8240 to behave as a PCI bus master

1

Memory space

0

This bit controls whether the MPC8240 (as a target) responds to memory

accesses.

0 The MPC8240 does not respond to PCI memory space accesses.

1 The MPC8240 responds to PCI memory space accesses.

0

I/O space

0

This bit is hardwired to 0, indicating that the MPC8240 (as a target) does

not respond to PCI I/O space accesses.

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...