Chapter 4. Configuration Registers

4-47

Memory Control Configuration Registers

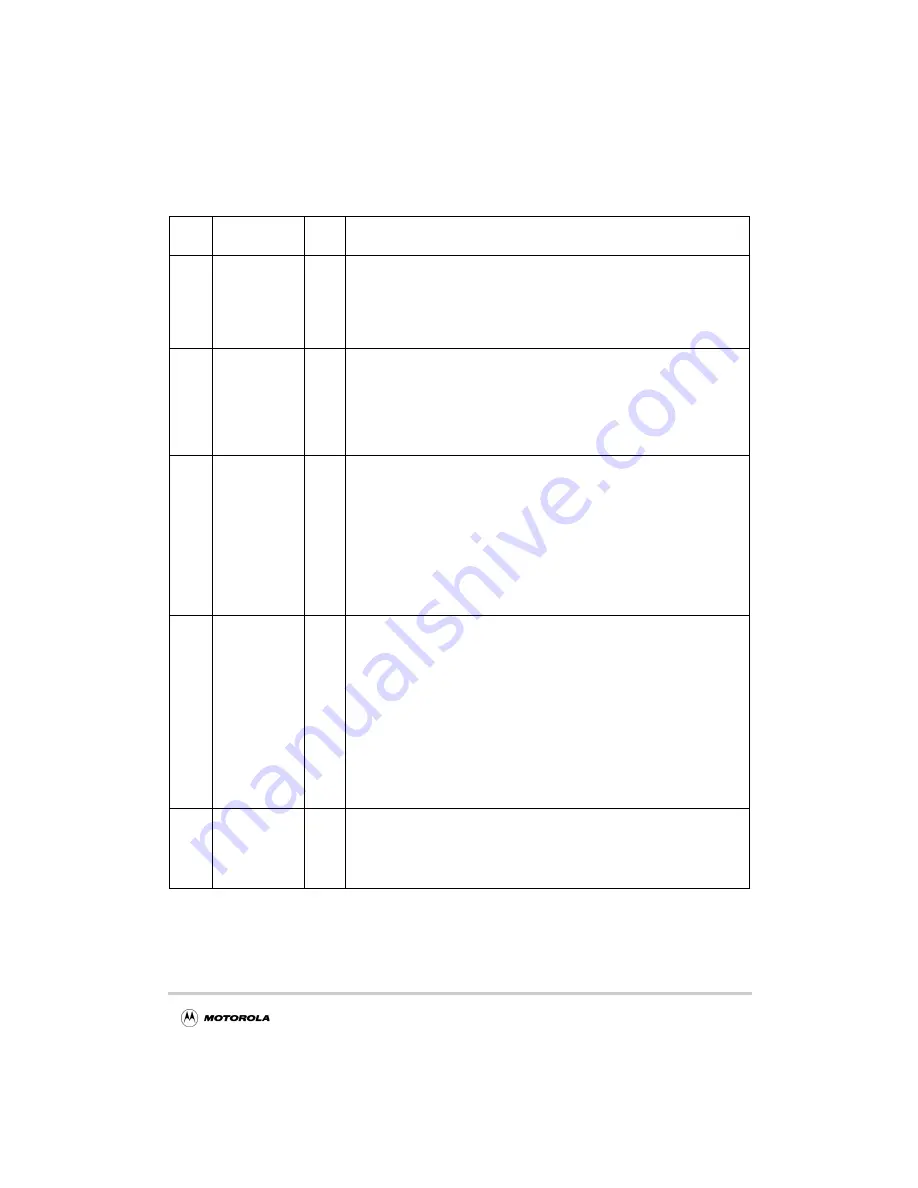

20

INLINE_PAR_

NOT_ECC

0

In-line parity —not ECC. This bit selects between the ECC and parity

checking/correction mechanisms of the in-line data path when performing memory

reads. This bit is applicable for SDRAM systems running in in-line buffer mode

(MCCR4[BUF_TYPE[0–1]] = 0b10) only, and when INLINE_RD_EN = 1.

0 MPC8240 uses ECC on the memory data bus.

1 MPC8240 uses parity on the memory data bus.

19

WRITE_

PARITY_

CHK

0

Write parity check enable. This bit controls whether the MPC8240 uses the parity

checking hardware in the data path to report peripheral bus parity errors on

memory system write operations. Write parity checking can be enabled for

SDRAM, FPM, or EDO systems running in any buffer mode. This bit activates

different parity checking hardware than that controlled by PCKEN.

0 peripheral bus write parity error reporting disabled

1 peripheral bus write parity error reporting enabled

18

INLINE_RD_ EN

0

In-line read parity or ECC check/correction enable. This bit controls whether the

MPC8240 uses the ECC/parity checking and/or correction hardware in the in-line

data path to report ECC or parity errors on memory system read operations. This

bit activates different parity/ECC checking/correction hardware than that controlled

by ECC_EN and PCKEN. Read parity/ECC checking can be enabled for SDRAM

systems running in in-line buffer mode (MCCR4[BUF_TYPE[0–1]] = 0b10) only.

Also, note that the INLINE_PAR_NOT_ECC bit selects between parity or ECC on

the memory data bus when this bit is set.

0 In-line memory bus read parity/ECC error reporting disabled

1 In-line memory bus read parity/ECC error reporting enabled. Note that

MCCR1[PCKEN] must be cleared when this bit is set.

17

ECC_EN

0

ECC enable. This bit controls whether the MPC8240 uses ECC for transactions to

system memory. ECC_EN should be set only for systems using FPM/EDO

memory. Note that the ECC_EN parameter overrides the PCKEN parameter. Also

note that this bit and RMW_PAR cannot both be set, and it is illegal to set this bit

with EDO = 1 and REGISTERED = 1. Systems using SDRAM use a different

(in-line) ECC hardware and therefore, must have ECC_EN = 0. See Section 6.2,

“SDRAM Interface Operation,” for more information.

When ECC_EN = 1, the processor should not be configured to check address or

data parity in the HID0 register. (See Section 5.3.1.2.1, “Hardware

Implementation-Dependent Register 0 (HID0).”

0 ECC disabled

1 ECC enabled

16

EDO

0

EDO enable. This bit indicates the type of DRAMs for the MPC8240 memory

interface. See Section 6.3, “FPM or EDO DRAM Interface Operation,” for more

information.

0 Indicates standard DRAMs

1 Indicates EDO DRAMs

Table 4-39. Bit Settings for MCCR2—0xF4 (Continued)

Bits

Name

Reset

Value

Description

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...