5-30

MPC8240 Integrated Processor User’s Manual

Memory Management

5.5.3 Exception Priorities

The exception priorities for the processor core are unchanged from those described in the

MPC603e User’s Manual except for the alignment exception, whose causes are prioritized

as follows:

1. Floating-point operand not word-aligned

2. lmw, stmw, lwarx, or stwcx operand not word-aligned

3. eciwx or ecowx operand misaligned

4. A multiple or string access is attempted with MSR[LE] set.

Also, there is a priority mechanism for all the conditions specific to the MPC8240 that can

cause a machine check exception. These are described in Chapter 13, “Error Handling.”

5.6 Memory Management

The following subsections describe the memory management features of the PowerPC

architecture and the MPC8240 implementation.

5.6.1 PowerPC MMU Model

The primary functions of the MMU are:

•

to translate logical (effective) addresses to physical addresses for memory accesses

•

to provide access protection on blocks and pages of memory

There are two types of accesses generated by the processor core that require address

translation—instruction accesses and data accesses to memory generated by load and store

instructions.

The PowerPC MMU and exception models support demand-paged virtual memory. Virtual

memory management permits execution of programs larger than the size of physical

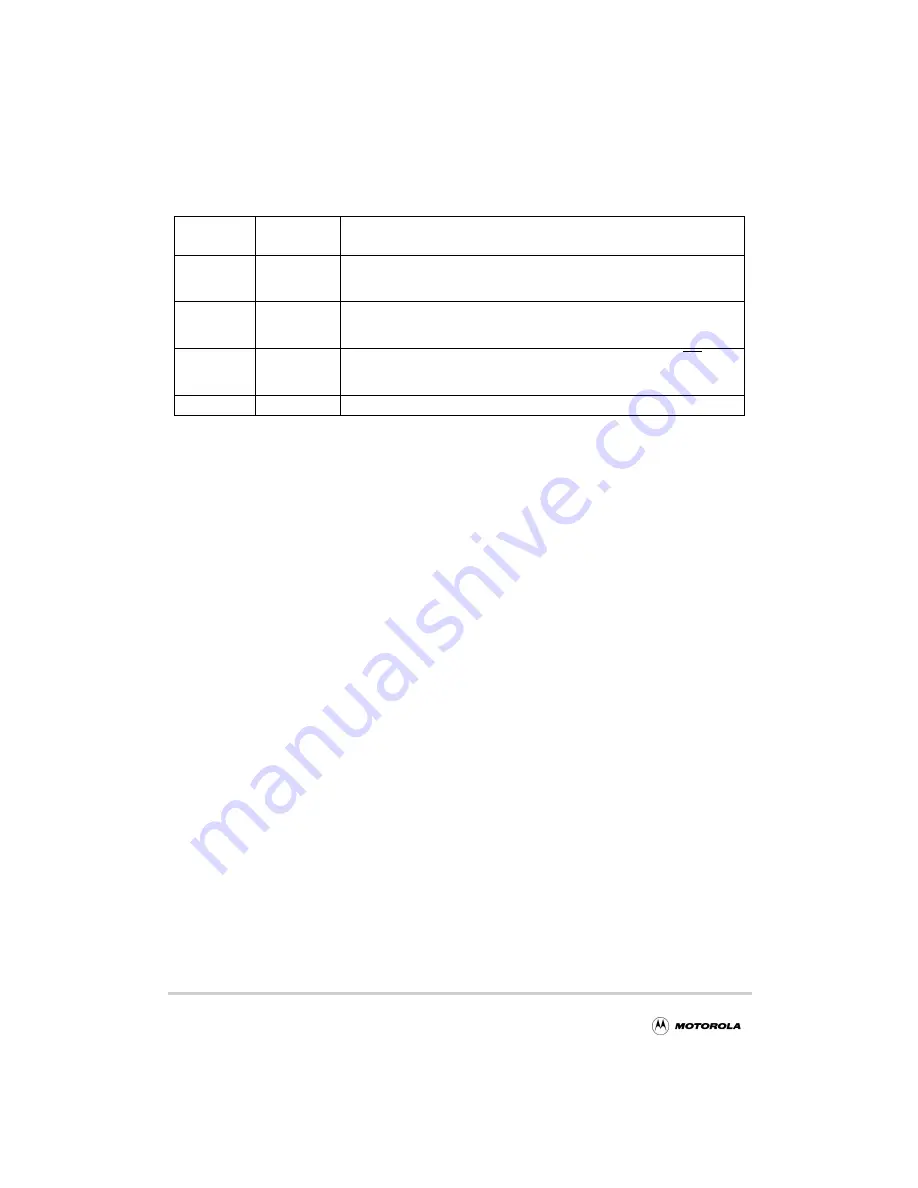

Data store

translation

miss

01200

A data store translation miss exception is caused when the effective address for a

data store operation cannot be translated by the DTLB, or when a DTLB hit occurs,

and the changed bit in the PTE must be set due to a data store operation.

Instruction

address

breakpoint

01300

An instruction address breakpoint exception occurs when the address (bits 0–29) in

the IABR matches the next instruction to complete in the completion unit, and the

IABR enable bit (bit 30) is set.

System

management

interrupt

01400

A system management interrupt is caused when MSR[EE] = 1 and the SMI input

signal is asserted.

Reserved

01500–02FFF

—

Table 5-8. Exceptions and Conditions (Continued)

Exception

Type

Vector Offset

(hex)

Causing Conditions

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...