Chapter 5. PowerPC Processor Core

5-35

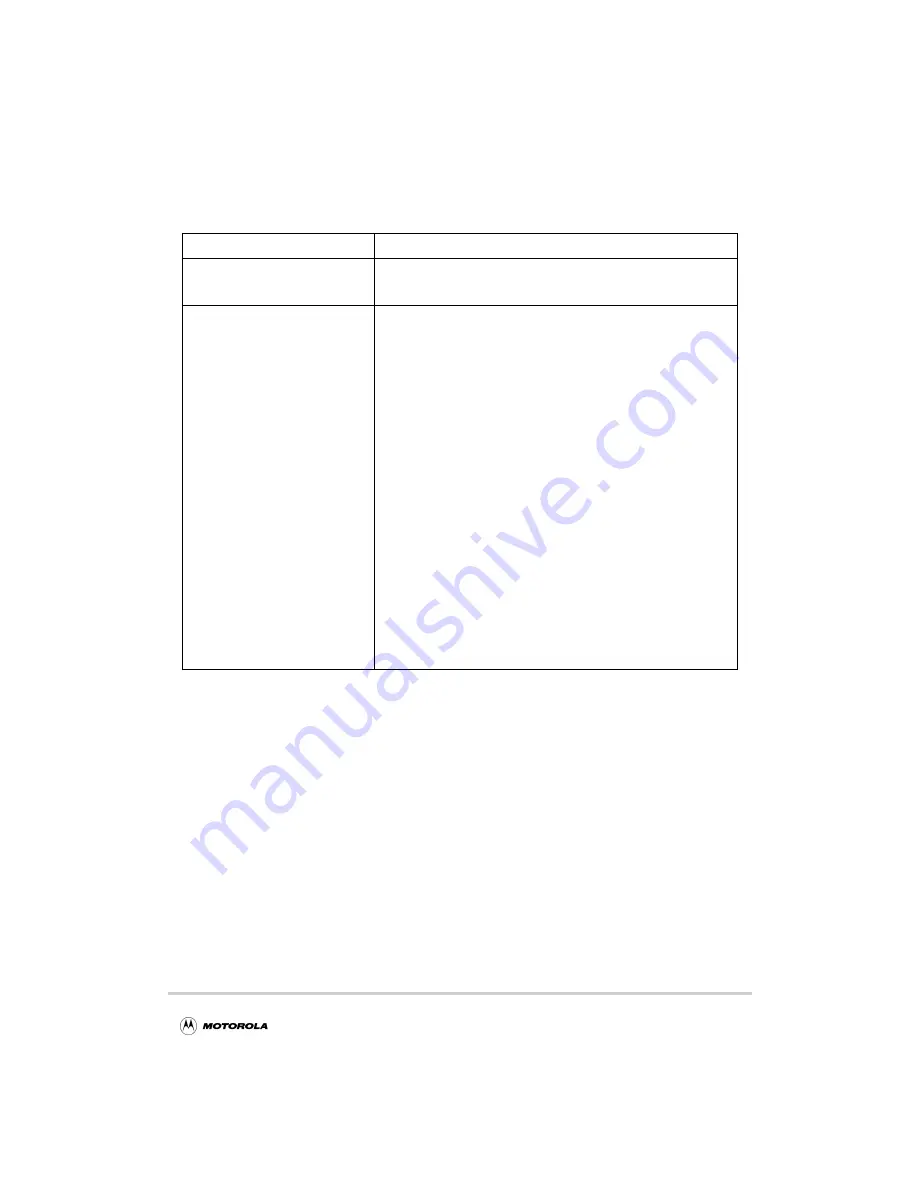

Differences between the MPC8240 Core and the PowerPC 603e Microprocessor

Areas of memory accessed by dcbz

instruction should not be marked as

global

This was previously documented as an anomaly in the MPC603e. Areas of

memory accessed by a dcbz instruction must be marked as not global in

the BAT or PTE.

All edits described in the MPC603e &

EC603e Microprocessor User’s

Manual Errata document

For example,

Note that incoherency may occur if a write-through store is followed by a

dcbz instruction that is in turn followed by a snoop, all to the same cache

block. This occurs when the logical address for the dcbz and the

write-through store are different but aliased to the same physical page.

To avoid potential adverse effects, dcbz should not be used to zero cache

blocks in memory marked as write-through that can be accessed through

multiple logical addresses. Explicit store instructions with data of zeroes

should be used instead.

Note that broadcasting a sequence of dcbz instructions may cause snoop

accesses to be retried indefinitely, which may cause the snoop originator

to time out or may cause the snooped transaction to not complete. This

can be avoided by disabling the broadcasting of dcbz by marking the

memory space being addressed by the dcbz instruction as not global in

the BAT or PTE.

Also,

Add the following text after the first paragraph of the sub-bullet for

Floating-point registers (FPRs):

Before the stfd instruction is used to store the contents of an FPR to

memory, the FPR must have been initialized after reset (explicitly loaded

with any value) by using a floating point load instruction.

These are just a few examples. Refer to the errata document for a

complete list.

Table 5-10. Major Differences between MPC8240’s Core and the MPC603e User’s

Manual (Continued)

Description

Impact

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...