6-18

MPC8240 Integrated Processor User’s Manual

SDRAM Interface Operation

•

Mode register set (for configuration)—Allows setting of SDRAM options. These

options are CAS latency, burst type, and burst length.

— CAS latency may be chosen as provided by the preferred SDRAM. (Some

SDRAMs provide CAS latency 1, 2, 3, some provide CAS latency 1, 2, 3, 4).

— Burst type must be set to sequential.

— Although some SDRAMs provide variable burst lengths of 1, 2, 4, 8 page size,

the MPC8240 supports only a burst length of 4 or 8. Burst length 4 must be

selected for operation with a 64 bit memory interface and 8-beat burst lengths are

used with a 32-bit memory interface. Burst lengths of 1 and 2 page size are not

supported by the MPC8240. This command is performed by the MPC8240

during system initialization.

The mode register data (CAS latency, burst length and burst type), is provided by

software at reset in the MPC8240 configuration register and is subsequently

transferred to the SDRAM array by the MPC8240after MEMGO is enabled.

•

Self refresh (for long periods of standby)—Used when the device will be in standby

for very long periods of time. Automatically generates internal refresh cycles to keep

the data in both memory banks refreshed. Before execution of this command, all

memory banks must be in a precharged state.

The MPC8240 automatically issues a precharge command to the SDRAM when the

BSTOPRE or PGMAX intervals have expired, regardless of pending memory transactions

from the PCI bus orprocessorcore. See Section 6.2.7, “SDRAM Page Mode,” for more

information about the BSTOPRE and PGMAX parameters. The MPC8240 can perform

precharge cycles concurrent with snoop broadcasts for PCI transactions.

6.2.6 SDRAM Burst and Single-Beat Transactions

In 64-bit data bus mode, the MPC8240 performs a four-beat burst for every transaction

(burst and single-beat); in 32-bit data bus mode, the MPC8240 performs an eight-beat burst

for every transaction (burst and single-beat). The burst is always sequential, and the critical

double word is always supplied first. For example, in 64-bit data bus mode, if the processor

core requests the third double word of a cache block, the MPC8240 reads double words

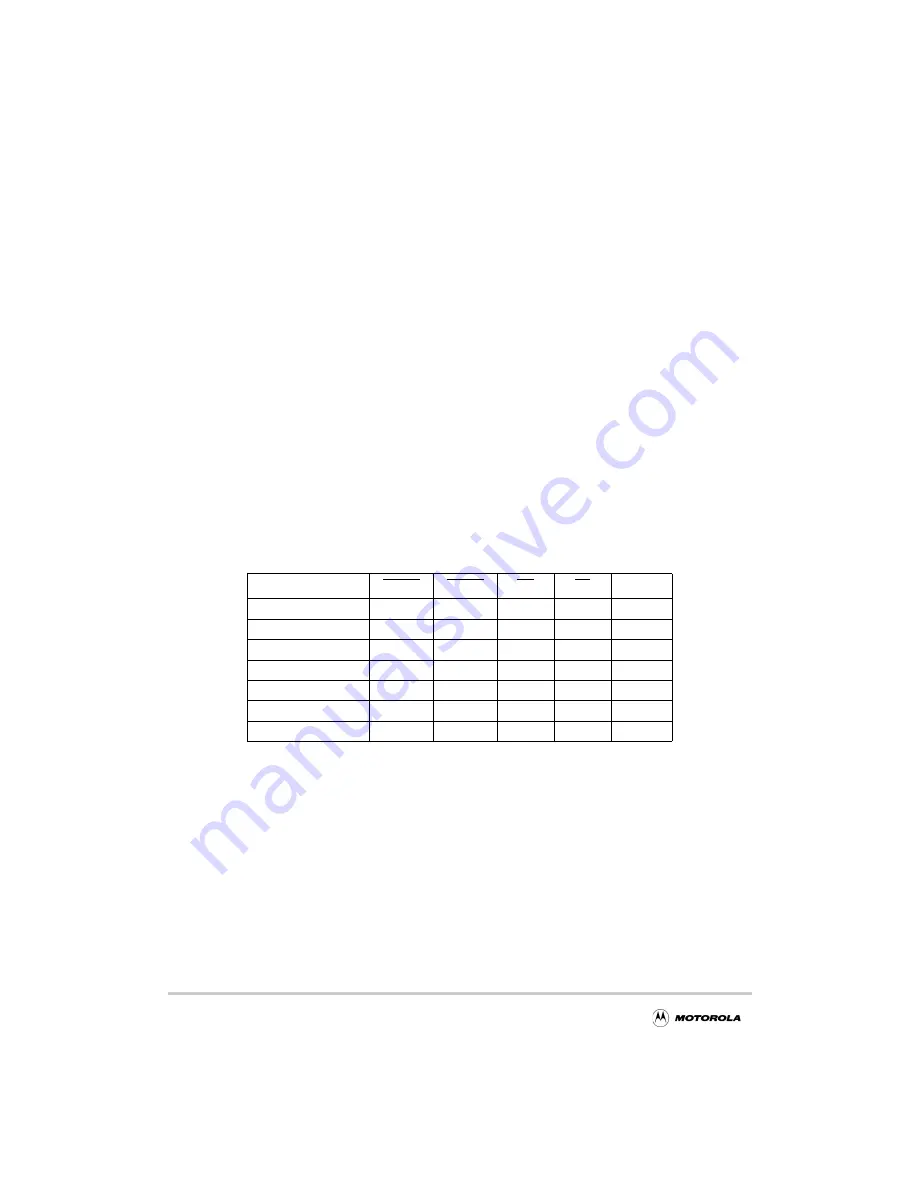

Table 6-10. MPC8240 SDRAM Interface Commands

Command

SDRAS

SDCAS

WE

CS

CKE

Bank activate

Asserted

Negated

Negated

Asserted

Asserted

Precharge

Asserted

Negated

Asserted

Asserted

Asserted

Read

Negated

Asserted

Negated

Asserted

Asserted

Write

Negated

Asserted

Asserted

Asserted

Asserted

CBR refresh

Asserted

Asserted

Negated

Asserted

Asserted

Mode register set

Asserted

Asserted

Asserted

Asserted

Asserted

Self refresh

Asserted

Asserted

Negated

Asserted

Negated

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...