Chapter 7. PCI Bus Interface

7-5

PCI Bus Arbitration

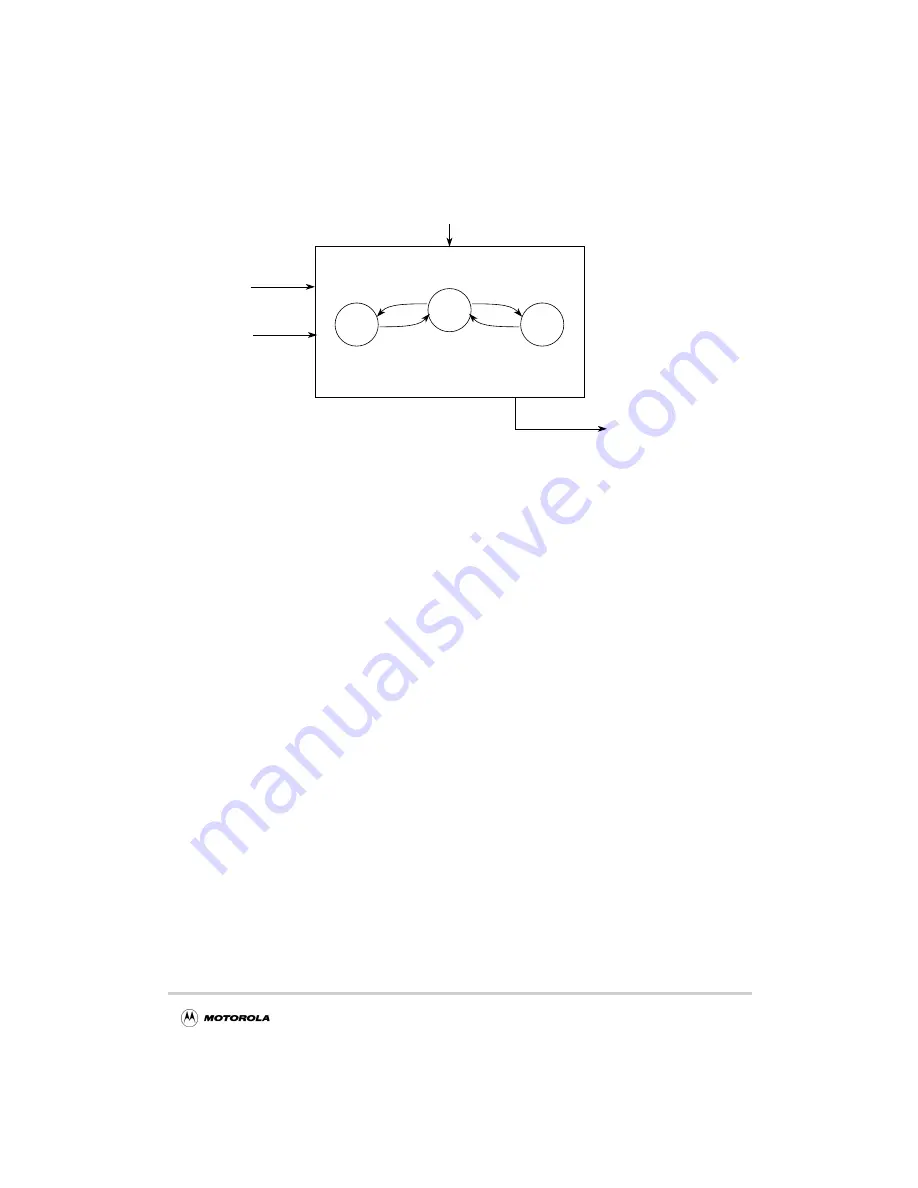

Figure 7-1. Internal Processor-DMA Arbitration for PCI Bus

As shown in Figure 7-1, the priorities propagate as follows: processor-DMA channel

0-processor-DMA channel 1-processor-DMA channel 0, and so on. Processor and DMA

transactions allow for rearbitration (arbiter state transitions) at PCI transaction boundaries.

7.2.1.1 Processor-Initiated Transactions to PCI Bus

The PCI transaction boundaries for processor-initiated transactions occur at the successful

completion of each processor transaction. Note that processor transactions to the PCI bus

may be interrupted before completion by the loss of mastership on the PCI bus or by the

PCI latency timer described in Section 4.2.6, “Latency Timer—Offset 0x0D.” However,

this case does not constitute a PCI transaction boundary, and when the MPC8240 regains

mastership of the external PCI bus, the processor transaction in progress continues without

rearbitration with the DMA controller.

7.2.1.2 DMA-Initiated Transactions to the PCI Bus

PCI transaction boundaries for DMA-initiated transactions allow for rearbitration (arbiter

state transitions) after the transmission of up to 4 Kbytes on the PCI bus. In order for a

DMA channel to stream (up to 4 Kbytes) between the local memory and the PCI bus, the

local memory interface (and the DMA queues) must also be available to sustain the

streaming. See Section 12.2, “Internal Arbitration,” for more information on priorities for

access to the local memory interface.

DMA streams (up to 4 Kbytes) from local memory to the PCI bus can cause both the local

memory and PCI interface to transfer up to 4 Kbytes without interruption. Additionally,

DMA transfers from PCI to local memory can cause up to 4 Kbytes to be read from the PCI

bus without interruption by the MPC8240. Note, however, that DMA writes (in this case,

from PCI) to local memory occur in increments of single cache lines at a time.

DMA 0

Processor core-

PCI Req/Gnt

Processor

DMA 0 PCI Req/Gnt

DMA 1 PCI Req/Gnt

MPC8240

PCI Req/Gnt

to PCI Bus Arbiter

DMA 1

1

2

4

3

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...