Chapter 8. DMA Controller

8-17

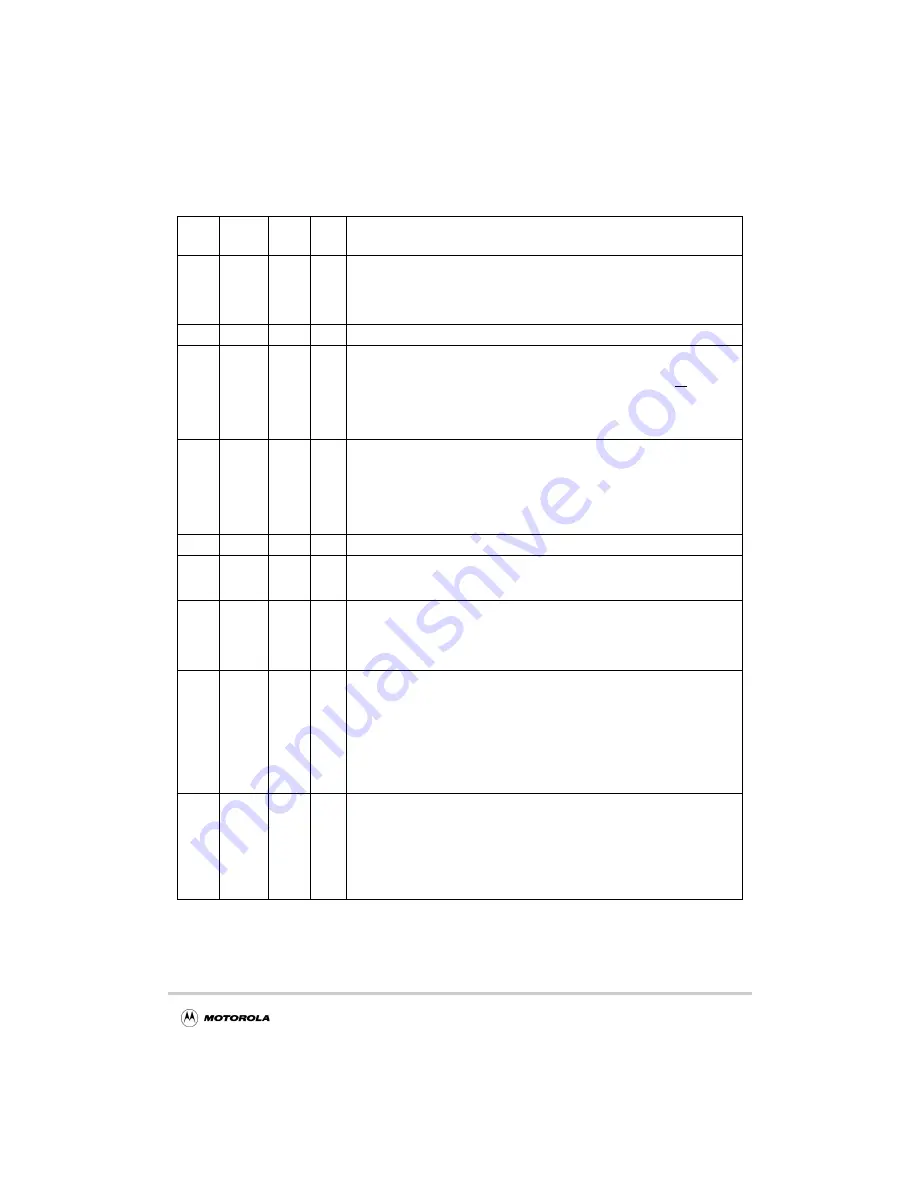

DMA Register Descriptions

11–10

PRC

00

RW

PCI Read Command. Indicates the types of PCI read command to be used.

00 PCI Read

01 PCI Read-line

10 PCI Read-multiple

11 Reserved

9

—

0

R

Reserved

8

EIE

0

RW

Error interrupt enable. Interrupt mechanism used depends on the setting of the

IRQS bit.

0 Disables error interrupts

1 Generates an interrupt to the processor core, through the internal int

mechanism and the EPIC unit, if there is a memory or PCI error during a DMA

transfer (signalled by the setting of LME or PE in the DSR).

7

EOTIE

0

RW

End-of-transfer interrupt enable. Interrupt mechanism used depends on the

setting of the IRQS bit.

0 Disables end-of-transfer interrupts

1 Generates an interrupt at the completion of a DMA transfer. (that is,

NDAR[EOTD] bit is set). For chained DMA, the interrupt is driven active at the

end of the last segment. For periodic DMA, the interrupt is driven at the end of

each periodic transfer event.

6–4

—

000

R

Reserved

3

DL

0

RW

Descriptor location

0 The descriptor is located in the local memory space.

1 The descriptor is located in the PCI memory space.

2

CTM

0

RW

Channel transfer mode

0 Chaining mode. See Section 8.3.2, “DMA Chaining Mode.”

1 Direct DMA mode. Software is responsible for placing all the required

parameters into the necessary registers to start the DMA process. See

Section 8.3.1, “DMA Direct Mode.”

1

CC

0

RW

Channel continue. This bit applies only to chaining mode and is cleared by the

MPC8240 after every descriptor read. It is typically set after software dynamically

adds more descriptors to a chain that is currently in progress or to a finished

chain. Note that it is not advisable to remove descriptors by setting this bit

because there is no deterministic way to predict when the DMA controller will

read a specific descriptor.

0 Channel stopped

1 The DMA transfer will restart the transferring process starting at the current

descriptor address (in CDAR).

0

CS

0

RW

Channel start. This bit is toggled by software.

0 to 1 transition when the channel is not busy (DSR[CB] = 0) starts the DMA

process. If the channel is busy and a 0 to 1 transition occurs, then the DMA

channel restarts from a previous halt condition.

1 to 0 transition when the channel is busy (DSR[CB] = 1) halts the DMA process.

Note that in chaining mode, it is not necessary to halt the channel to modify a

descriptor because descriptors can be modified by setting the DMR[CC] bit.

Nothing happens if the channel is not busy and a 1 to 0 transition occurs.

Table 8-3. DMR Field Descriptions—Offsets 0x100, 0x200 (Continued)

Bits

Name

Reset

Value

R/W

Description

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...