10-8

MPC8240 Integrated Processor User’s Manual

I

2

C Register Descriptions

Table 10-3 describes the bit settings of I2CADR.

10.3.2 I

2

C Frequency Divider Register (I2CFDR)

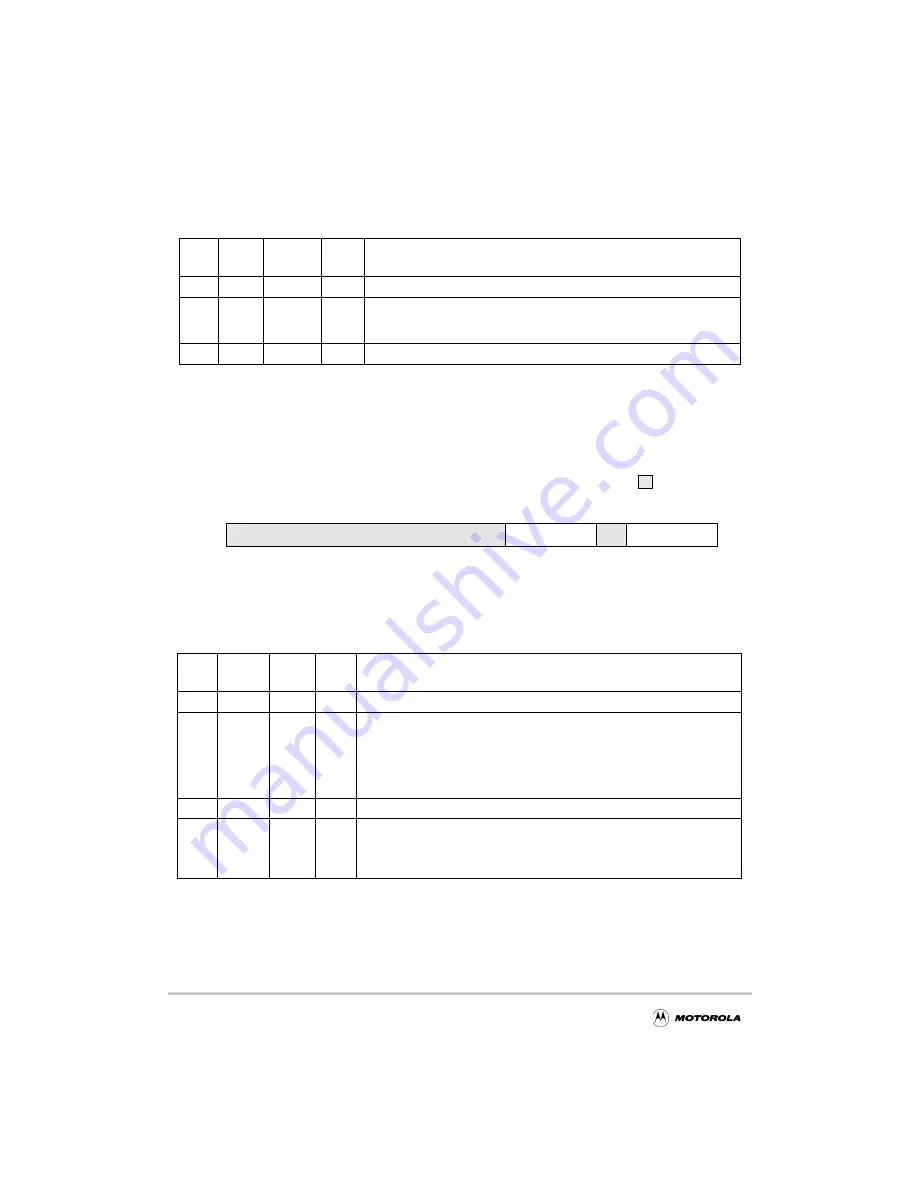

The I2CFDR, shown in Figure 10-4, configures the sampling rate and the clock bit rate for

the I

2

C unit.

Figure 10-4. I

2

C Frequency Divider Register (I2CFDR)

Table 10-4 describes the bit settings of the I2CFDR.

Table 10-3. I2CADR Field Descriptions—Offset 0x0_3000

Bits

Name

Reset

Value

R/W

Description

31–8

—

All zeros

R

Reserved

7–1

ADDR

0x00

R/W

Slave address. Contains the specific address to which the MPC8240

responds as a slave on the I

2

C interface. Note that the default mode of the

I

2

C interface is slave mode for an address match.

0

—

0

R

Reserved

Table 10-4. I2CFDR Field Descriptions—Offset 0x0_3004

Bits

Name

Reset

Value

R/W

Description

31–14

—

All 0s

R

Reserved

13–8

DFFSR

0x10

R/W

Digital filter frequency sampling rate—To assist in filtering out signal noise, the

sample rate is programmable; this field is used to prescale the frequency at

which the digital filter takes samples from the I

2

C bus. The resulting sampling

rate is the local memory frequency (SDRAM_CLK) divided by the non-zero

value set in this field. If DFFSR is set to zero, the I

2

C bus sample points default

to the reset divisor 0x10.

7–6

—

00

R

Reserved

5–0

FDR

0x00

R/W

Frequency divider ratio—Used to prescale the clock for bit rate selection. The

serial bit clock frequency of SCL is equal to the local memory clock

(SDRAM_CLK) divided by the divider shown in Table 10-5. Note that the

frequency divider value can be changed at any point in a program.

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

DFFSR

0 0

FDR

31

14 13

8

7

6

5

0

Reserved

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...