11-18

MPC8240 Integrated Processor User’s Manual

Register Definitions

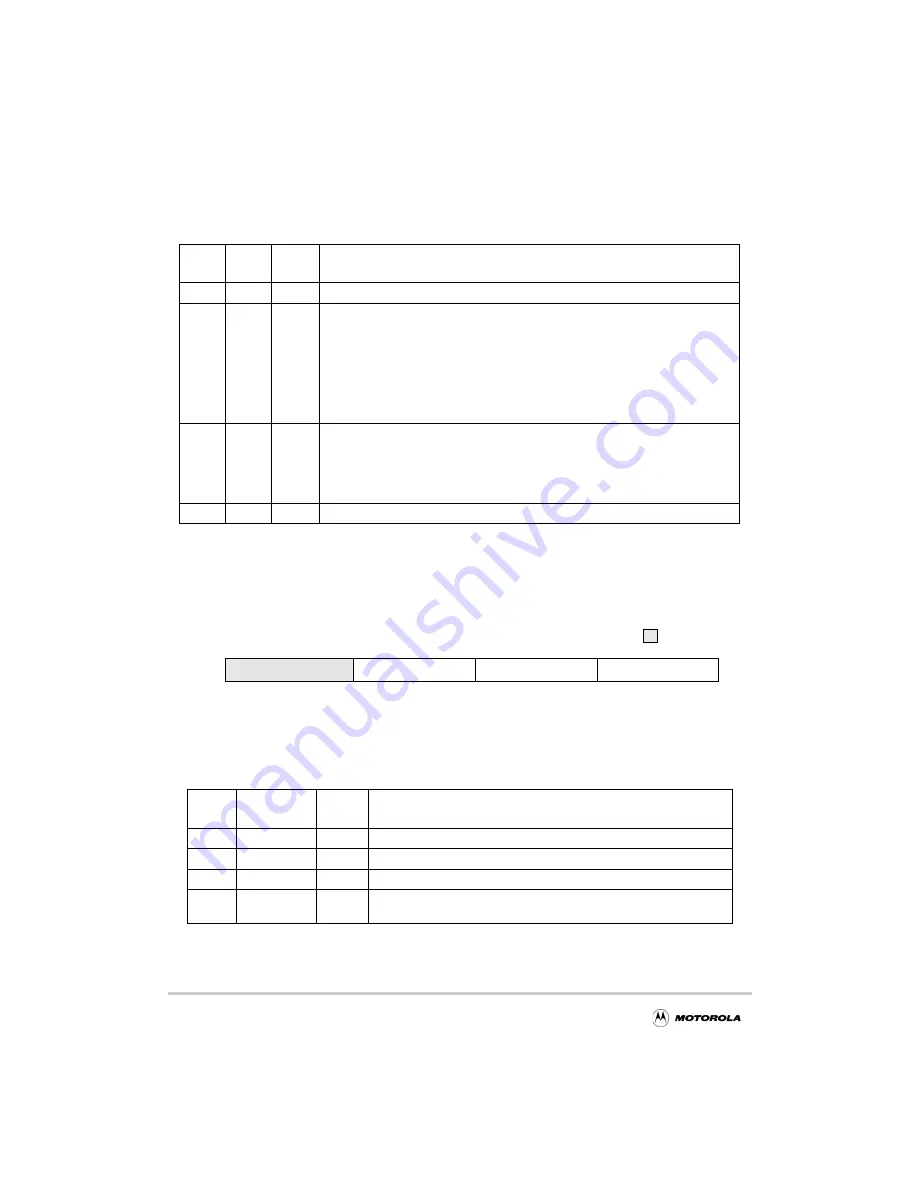

Table 11-7 describes the bit settings for the EICR.

11.9.4 EPIC Vendor Identification Register (EVI)

The EVI has specific read-only information about the vendor and the device revision.

Figure 11-7 shows the bits in the EVI.

Figure 11-7. EPIC Vendor Identification Register (EVI)

Table 11-8 describes the bit settings for the EVI.

Table 11-7. EICR Field Descriptions—Offset 0x4_1030

Bits

Name

Reset

Value

Description

31

—

0

Reserved

30–28

R

0x4

Clock ratio. The S_CLK signal is driven by EPIC at a frequency of the SDRAM_CLK

frequency divided by twice the value of this 3-bit field. The reset value of this field is

0x4. At this value, the S_CLK signal operates at 1/8th the frequency of the

SDRAM_CLK signal. The allowable range of values for this field is between 1 and 7

resulting in a clock division ratio between 2 and 14 respectively.

Note that an illegal value could result in spurious vectors returned when in either direct

or serial mode.

27

SIE

0

Serial interrupt enable. This bit selects whether the MPC8240 IRQ signals are

configured for direct interrupts or serial interrupts. The GCR[M] must be set to 1

(mixed-mode) in order for this bit value to have meaning.

0 Direct interrupts mode

1 Serial interrupts mode

26–0

—

All 0s

Reserved

Table 11-8. EVI Register Field Descriptions—Offset 0x4_1080

Bits

Name

Reset

Value

Description

31–24

—

All 0s

Reserved

23–16

STEP

0x01

Stepping. This indicates the stepping (silicon revision) for this device.

15–8

DEVICE_ID

All 0s

Device identification

7–0

VENDOR_ID

All 0s

Vendor identification. Because this value is zeros, the MPC8240 is

considered to be a generic PIC-compliant device.

0 0 0 0 0 0 0 0

STEP

DEVICE_ID

VENDOR_ID

31

24 23

16 15

8

7

0

Reserved

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...