Chapter 11. Embedded Programmable Interrupt Controller (EPIC) Unit

11-23

Register Definitions

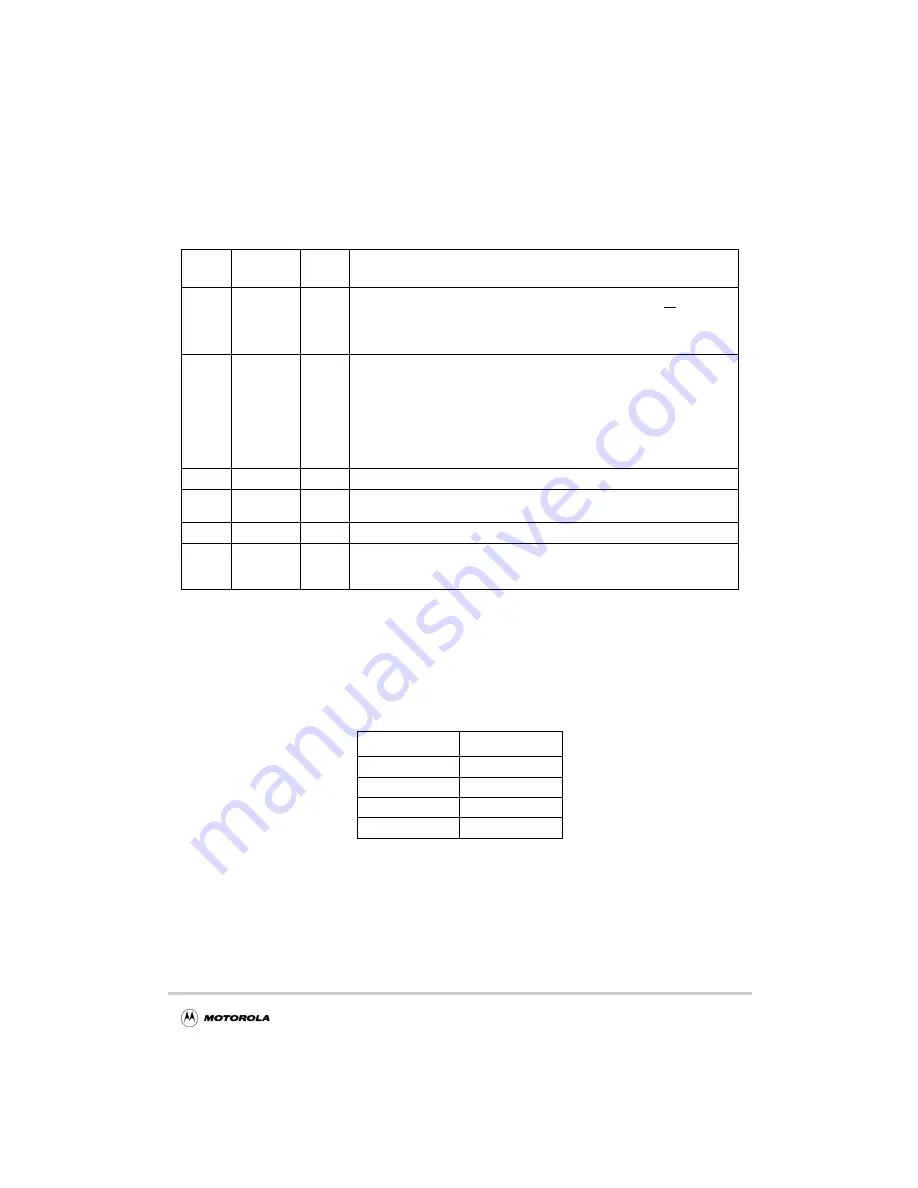

Table 11-17 describes the bit settings for the GTVPRs.

11.9.7.5 Global Timer Destination Registers (GTDRs)

Each GTDR indicates the destination for the timer’s interrupt. Because the MPC8240’s

EPIC unit supports a single processor, the destination is always P0. Note that this register

is read-only. The address offsets from EUMBBAR for the GTDRs are described in

Table 11-18.

Table 11-17. GTVPR Field Descriptions

Bits

Name

Reset

Value

Description

31

M

1

Mask. Mask interrupts from this timer

0 If the mask bit is cleared while the corresponding IPR bit is set, int is asserted

to the processor.

1 Further interrupts from this timer are disabled

30

A

0

Activity. Indicates that an interrupt has been requested or that it is in-service.

Note that this bit is read-only.

0 No current interrupt activity associated with this timer.

1 The interrupt bit for this timer is set in the IPR or ISR.

The VECTOR and PRIORITY values should not be changed while the A bit is

set.

29–20

—

All 0s

Reserved

19–16

PRIORITY

0x0

Priority. This field contains the four-bit interrupt priority. The lowest priority is 0

and the highest is 15. A priority level of 0 disables interrupts from this timer.

15–8

—

0x00

Reserved

7–0

VECTOR

0x00

Vector. The vector value in this field is returned when the interrupt acknowledge

register (IACK) is read, and the interrupt associated with this vector has been

requested.

Table 11-18. EUMBBAR Offsets for GTDRs

GTDR

Offset

GTDR0

0x4_1130

GTDR1

0x4_1170

GTDR2

0x4_11B0

GTDR3

0x4_11F0

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...