11-26

MPC8240 Integrated Processor User’s Manual

Register Definitions

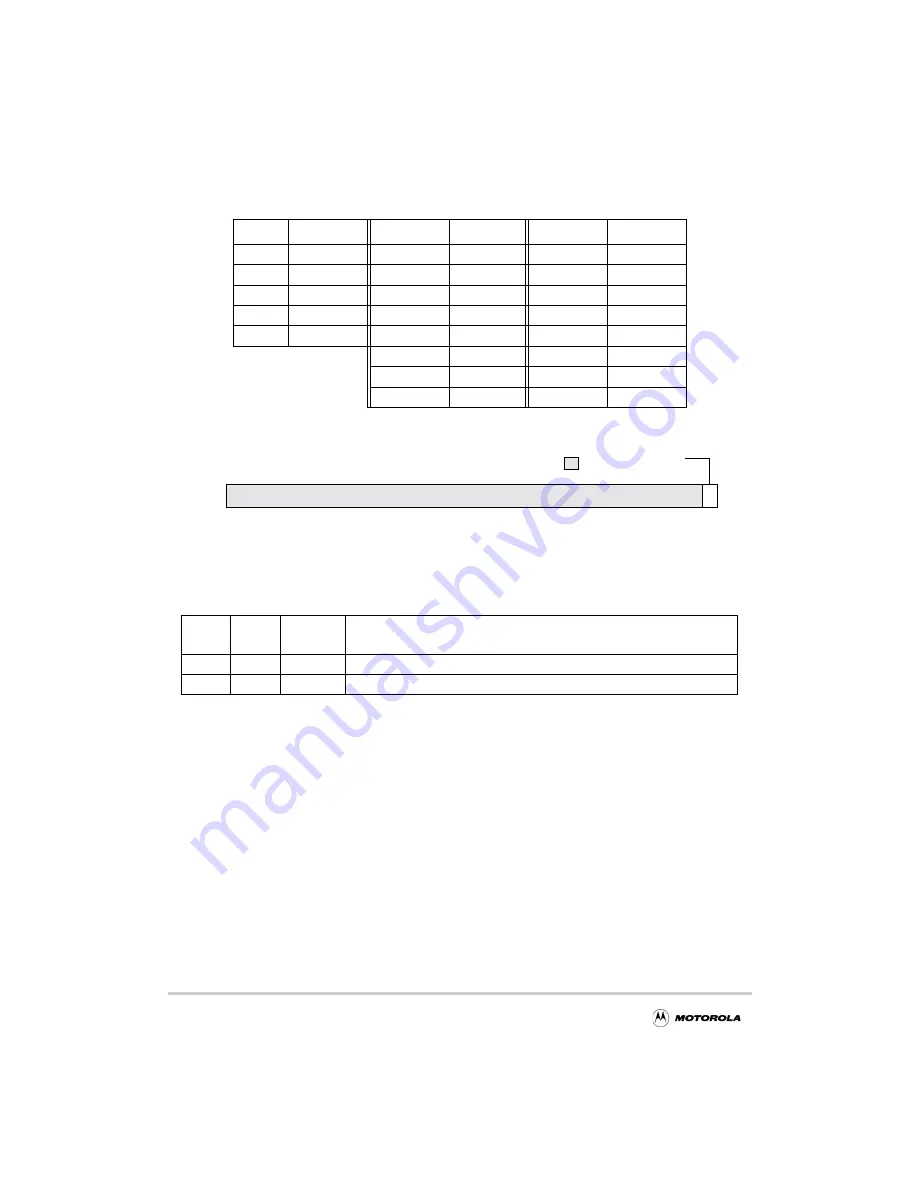

Figure 11-16 shows the bits of the IDRs and SDRs.

Figure 11-16. Direct and Serial Destination Registers (IDR and SDR)

Table 11-23 shows the bit settings for the IDRs and SDRs.

11.9.8.3 Internal (I

2

C, DMA, MU) Interrupt Vector/Priority Registers

(IIVPRs)

The IIVPRs have the same format and field descriptions as the GTVPRs, except that they

apply to the internal MPC8240 interrupt sources—the I

2

C unit, DMA unit (2 channels), and

MU. See Section 11.9.7.4, “Global Timer Vector/Priority Registers (GTVPRs),” for a

complete description of the GTVPRs.

11.9.8.4 Internal (I

2

C, DMA or MU) Interrupt Destination Registers

(IIDRs)

The IIDRs have the same format and field descriptions as the IDRs (and SDRs), except that

they apply to the internal MPC8240 interrupt sources—the I

2

C unit, DMA unit (2

channels), and MU. See Section 11.9.8.2, “Direct & Serial Interrupt Destination Registers

(IDRs, SDRs),” for a complete description of the IDRs.

Table 11-22. EUMBBAR Offsets for IDRs and SDRs

IDR

Offset

SDR

Offset

SDR

Offset

IDR0

0x5_0210

SDR0

0x5_0210

SDR8

0x5_0310

IDR1

0x5_0230

SDR1

0x5_0230

SDR9

0x5_0330

IDR2

0x5_0250

SDR2

0x5_0250

SDR10

0x5_0350

IDR3

0x5_0270

SDR3

0x5_0270

SDR11

0x5_0370

IDR4

0x5_0290

SDR4

0x5_0290

SDR12

0x5_0390

SDR5

0x5_02B0

SDR13

0x5_03B0

SDR6

0x5_02D0

SDR14

0x5_03D0

SDR7

0x5_02F0

SDR15

0x5_03F0

Table 11-23. IDR and SDR Field Descriptions

Bits

Name

Reset

Value

Description

31–1

—

All 0s

Reserved

0

P0

1

Processor 0. Direct and serial interrupts always directed to the processor.

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

31

1

0

Reserved

P0

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...