Chapter 15. Debug Features

15-11

Memory Interface Valid (MIV)

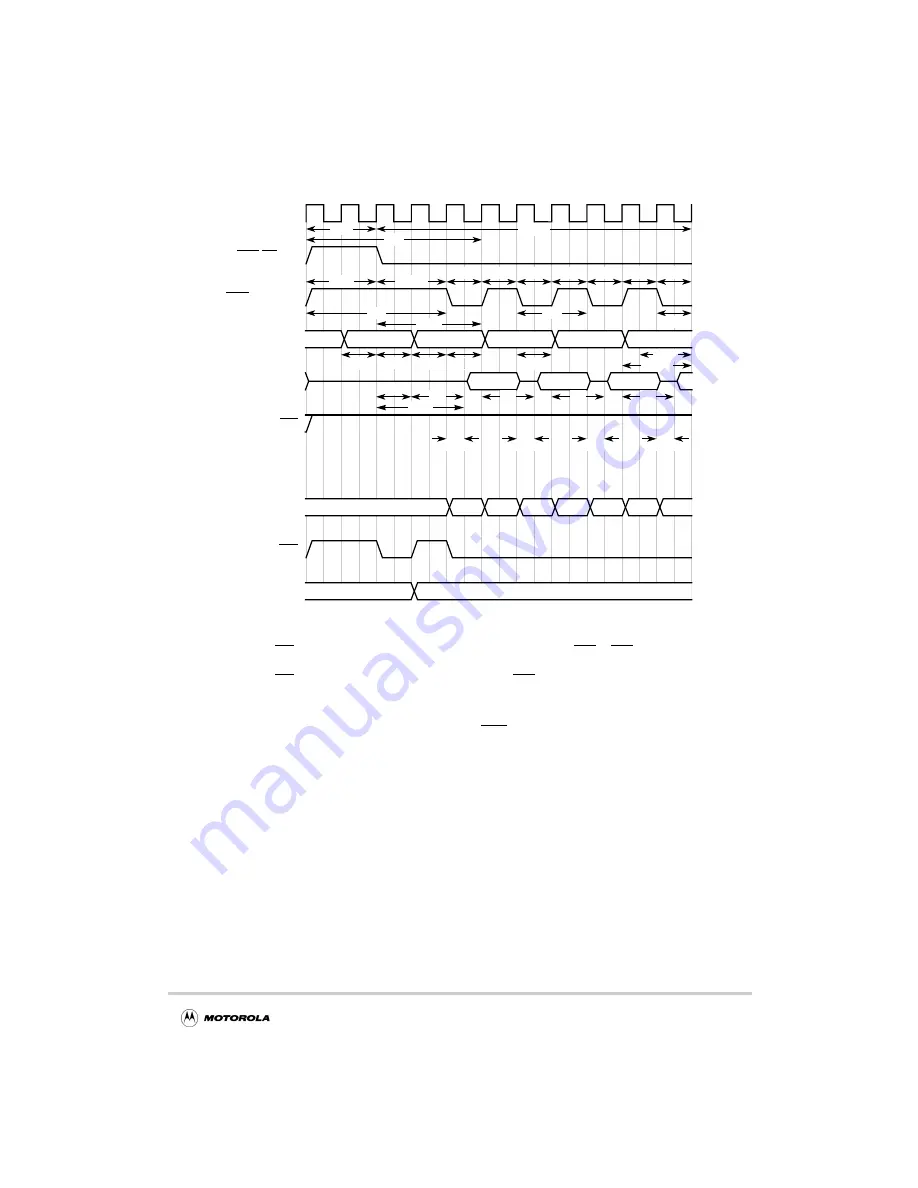

Figure 15-10. Example EDO Debug Address, MIV, and MAA Timings for Burst Read

Operation

NOTES

:

1. Subscripts identify programmable timing variables (RP1, RCD2, CAS3).

2. MIV asserts for address and control on the first clock cycle that RAS or CAS is asserted

for a read.

3. MIV asserts for data on the same clock cycle that CAS negates for a read.

SDRAM_CLK[0::3]

RAS/CS[0:7]

CAS/DQM[0:7]

ADDRESS

DATA

WE

DEBUG ADDRESS

MAA

MIV

RP

1

RC

RASP

CRP

RCD

2

CAS

3

CP

4

CP

4

CAS

5

CAS

5

CP

CSH

PC

ASR

ASC

CAH

CAH

RAH

ROW

COL

VALID

VALID

COL

COL

COL

CAS

5

CP

4

VALID

VALID

VALID

RSH

RAL

RHCP

DATA0

DATA0

RAD

CAC

AA

AA

AA

RAC

AA

DATA0

CAC

CAC

CAC

DA

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...