A-2

MPC8240 Integrated Processor User’s Manual

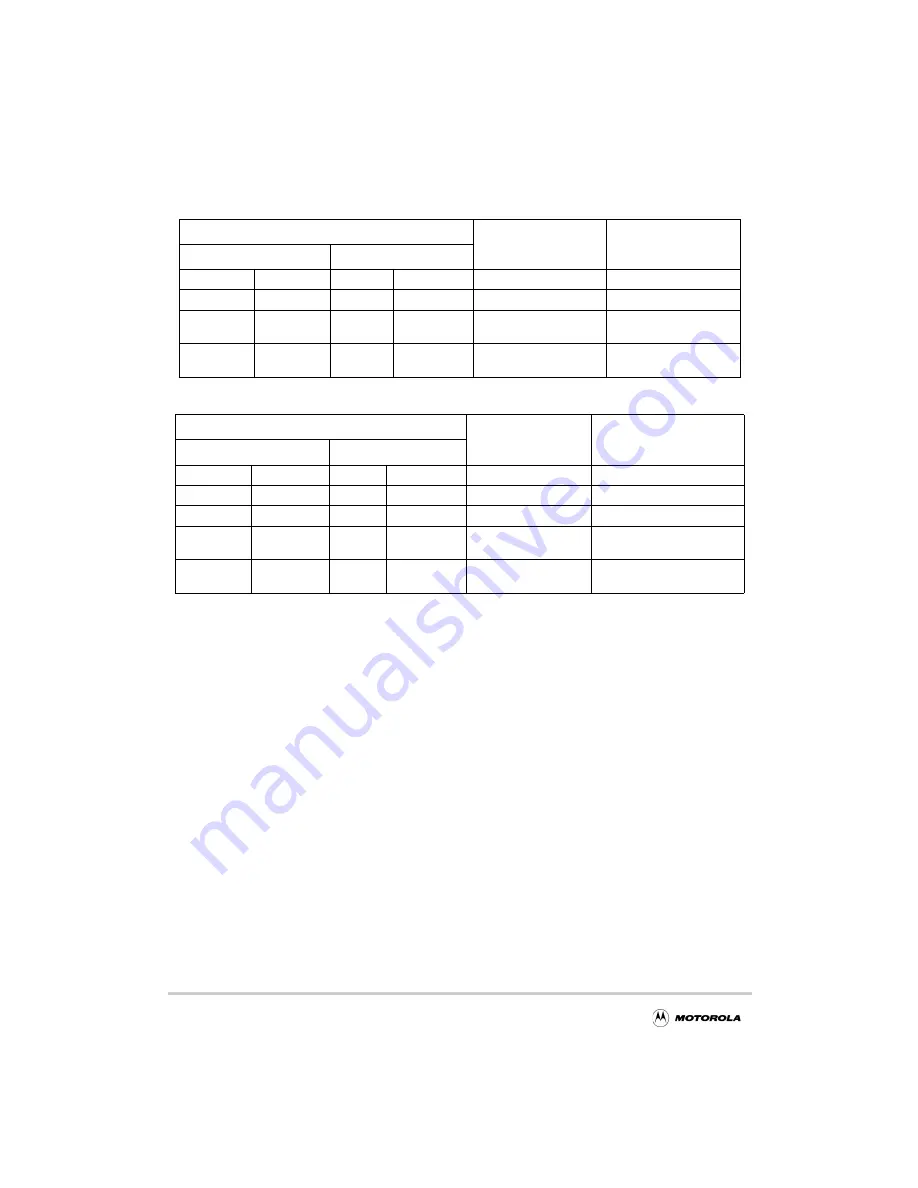

Address Space for Map A

Notes:

1 PCI configuration accesses to CF8 and CFC–CFF are handled as specified in the PCI Local Bus Specification.

See Section 7.4.5.2, “Accessing the PCI Configuration Space,” for more information on how the MPC8240

accesses PCI configuration space.

2. Processor addresses are translated to PCI addresses as follows:

PCI address (AD[31:0]) = 0b0 || A[1:31]. PCI configuration accesses use processor addresses

0x8000_0CF8 and 0x8000_0CFC–8000_0CFF.

Note that only 64 Kbytes (0x8000_0000–0x8000_FFFF) has been defined. The remainder of the region is

reserved for future use.

3. IDSEL for direct access method: 11 = 0x8080_08xx, 12 = 0x8080_10xx,..., 18 = 0x8084_00xx. See

Section 7.4.5.2, “Accessing the PCI Configuration Space.”

4. If the ROM is local, the MPC8240 ROM interface handles the access to local ROM. If ROM is remote, then the

MPC8240 generates a PCI memory transaction in the range 0xFF00_0000 to 0xFFFF_FFFF.

5. If the ROM is local, this space is reserved and accesses to it cause a memory select/Flash write error. If the

ROM is remote, then this space maps to PCI memory space.

Table A-2. Map A—PCI Memory Master View

PCI Memory Transactions Address Range

Processor Core

Address Range

Definition

Hex

Decimal

0000_0000

7FFF_FFFF

0

2G - 1

No local memory cycle

PCI memory space

8000_0000

BFFF_FFFF

2G

3G - 1

0000_0000–3EFF_FFFF

Local memory space

C000_0000

FEFF_FFFF

3G

4G - 16M - 1

No local memory cycle

Reserved (causes

memory select error)

FF00_0000

FFFF_FFFF

4G - 16M

4G - 1

No local memory cycle

ROM space (reserved if

ROM is local)

5

Table A-3. Address Map A—PCI I/O Master View

PCI I/O Transactions Address Range

Processor Core

Address Range

Definition

Hex

Decimal

0000_0000

0000_FFFF

0

64K - 1

No local memory cycle

Addressable by the processor

0001_0000

007F_FFFF

64K

8M - 1

No local memory cycle

Reserved

2

0080_0000

3F7F_FFFF

8M

1G - 8M - 1

No local memory cycle

Addressable by the processor

3F80_0000

3FFF_FFFF

1G - 8M

1G - 1

No local memory cycle

Not addressable by the

processor

4000_0000

FFFF_FFFF

1G

4G - 1

No local memory cycle

Not addressable by the

processor

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...