Appendix B. Bit and Byte Ordering

B-3

Big-Endian Mode

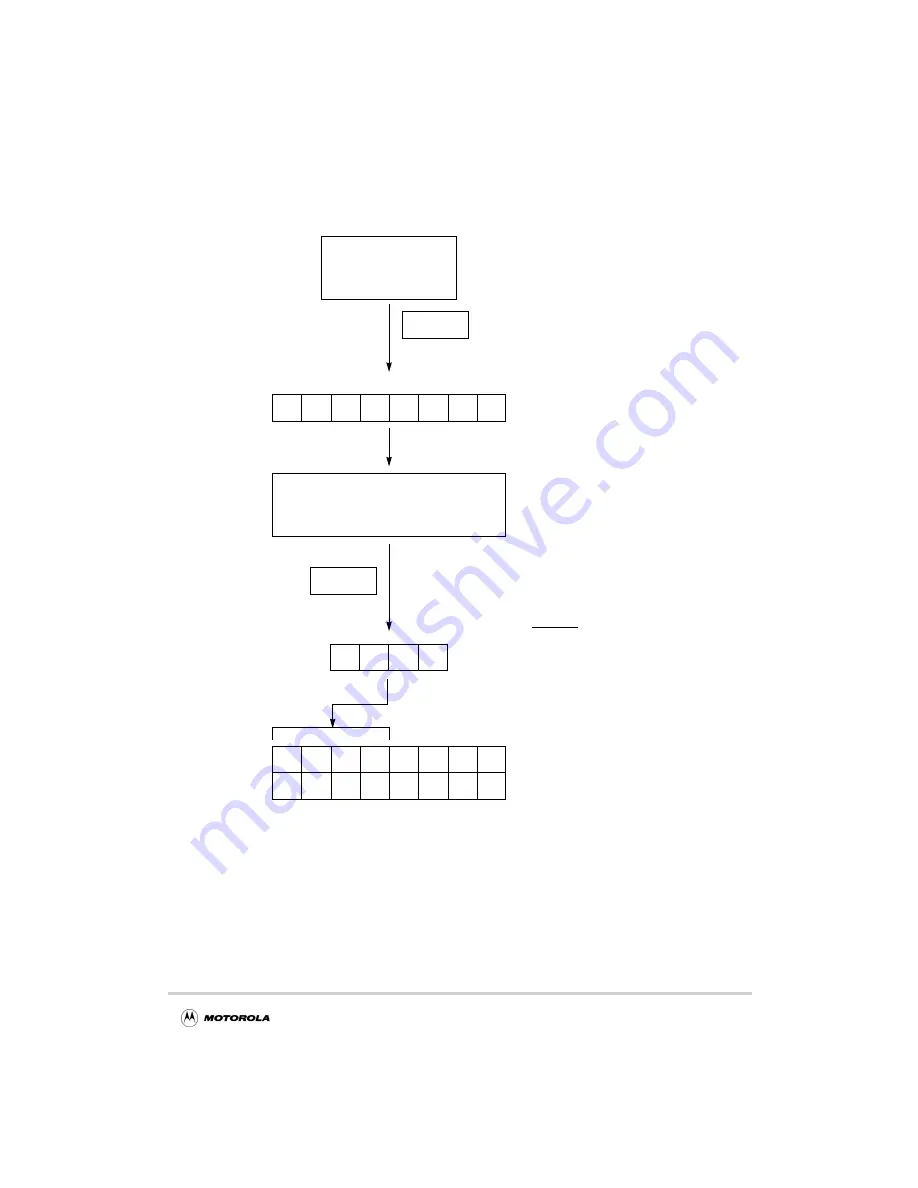

Figure B-1 shows a 4-byte write to PCI memory space in big-endian mode.

Figure B-1. Four-Byte Transfer to PCI Memory Space—Big-Endian Mode

Note that the MSB on the internal peripheral logic bus, D0, is placed on byte lane 0

(AD[7–0]) on the PCI bus. This occurs so D0 appears at address 0xnnnn_nn00 and not at

address 0xnnnn_nn03 in the PCI space.

Processor

0 0 0 0

0

1

2

3

4

5

6

7

D0

D1

D2

D3

xx

xx

xx

xx

3

2

1

0

D3

D2

D1

D0

D3

D2

D1

D0

0x00

0x08

PCI Big-Endian Memory Space

Byte lanes

PCI byte lanes (C/BE[3–0] asserted)

0 0 0 0

AD[3–0]

During address phase

(AD[1–0] = 0b00 for memory space access)

Runs PCI memory transaction

PCI data bus

(AD[7–0], AD[15–8], AD[23–16], and AD[31–24]

during data phase)

Core

PA[28–31]

Internal peripheral logic data bus

CDU

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...