E-26

MPC8240 Integrated Processor User’s Manual

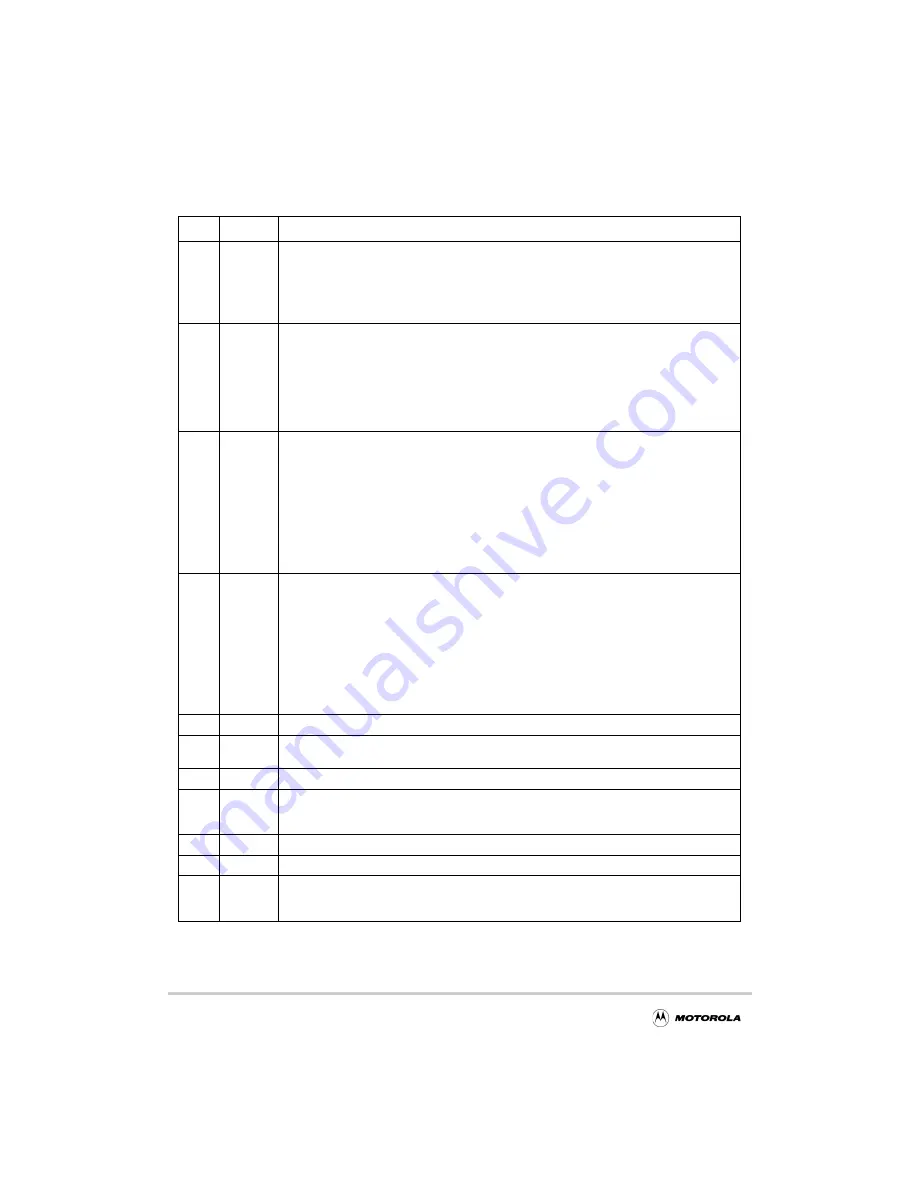

MPC8240-Specific Registers

18

ILOCK

Instruction cache lock

0 Normal operation

1 Instruction cache is locked. A locked cache supplies data normally on a hit, but an access is

treated as a cache-inhibited transaction on a miss. On a miss, the transaction to the bus is

single-beat.

To prevent locking during a cache access, an isync must precede the setting of ILOCK.

19

DLOCK

Data cache lock

0 Normal operation

1 Data cache is locked. A locked cache supplies data normally on a hit but an access is treated

as a cache-inhibited transaction on a miss. On a miss, the transaction to the bus is

single-beat.

A snoop hit to a locked L1 data cache performs as if the cache were not locked. A cache block

invalidated by a snoop remains invalid until the cache is unlocked.

To prevent locking during a cache access, a sync must precede the setting of DLOCK.

20

ICFI

Instruction cache flash invalidate

2

0 The instruction cache is not invalidated. The bit is cleared when the invalidation operation

begins (usually the next cycle after the write operation to the register). The instruction cache

must be enabled for the invalidation to occur.

1 An invalidate operation is issued that marks the state of each instruction cache block as

invalid without writing back modified cache blocks to memory. Cache access is blocked during

this time. Accesses to the cache from the peripheral logic bus are signaled as a miss during

invalidate-all operations. Setting ICFI clears all the valid bits of the blocks and the PLRU bits

to point to way L0 of each set. Once this flash invalidate bit is set through an mtspr

instruction, hardware automatically resets this bit in the next cycle (provided that the

corresponding cache enable bit is set in HID0).

21

DCFI

Data cache flash invalidate

2

0 The data cache is not invalidated. The bit is cleared when the invalidation operation begins

(usually the next cycle after the write operation to the register). The data cache must be

enabled for the invalidation to occur.

1 An invalidate operation is issued that marks the state of each data cache block as invalid

without writing back modified cache blocks to memory. Cache access is blocked during this

time. Accesses to the cache from the peripheral logic bus are signaled as a miss during

invalidate-all operations. Setting DCFI clears all the valid bits of the blocks and the PLRU bits

so that they point to way L0 of each set. Once the flash invalidate bit is set through an mtspr

instruction, hardware automatically resets this bit in the next cycle (provided that the

corresponding cache enable bit is set in HID0).

22–23

—

Reserved

24

—

IFEM bit on some other PowerPC devices

This bit is not used in the MPC8240 (and so it is reserved).

25–26

—

Reserved

27

FBIOB

Force branch indirect on bus

0 Register indirect branch targets are fetched normally

1 Forces register indirect branch targets to be fetched externally.

28

—

Reserved—Used as address broadcast enable bit on some other PowerPC devices

29–30

—

Reserved

31

NOOPTI

No-op the data cache touch instructions

0 The dcbt and dcbtst instructions are enabled.

1 The dcbt and dcbtst instructions are no-oped globally.

1

See Chapter 9, “Power Management,” of the MPC603e User’s Manual for more information.

2

See Chapter 3, “Instruction and Data Cache Operation,” of the MPC603e User’s Manual for more information.

Table E-20. HID0 Field Descriptions (Continued)

Bits

Name

Description

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...