3-2

MPC8240 Integrated Processor User’s Manual

Address Map B

Table 3-1, Table 3-2, Table 3-3, and Table 3-4 show separate views of address map B for

the processor core, a PCI memory device (host mode), a PCI memory device (agent mode),

and a PCI I/O device, respectively. When configured for map B, the MPC8240 translates

addresses across the internal peripheral logic bus and the external PCI bus as shown in

Figure 3-1 through Figure 3-3.

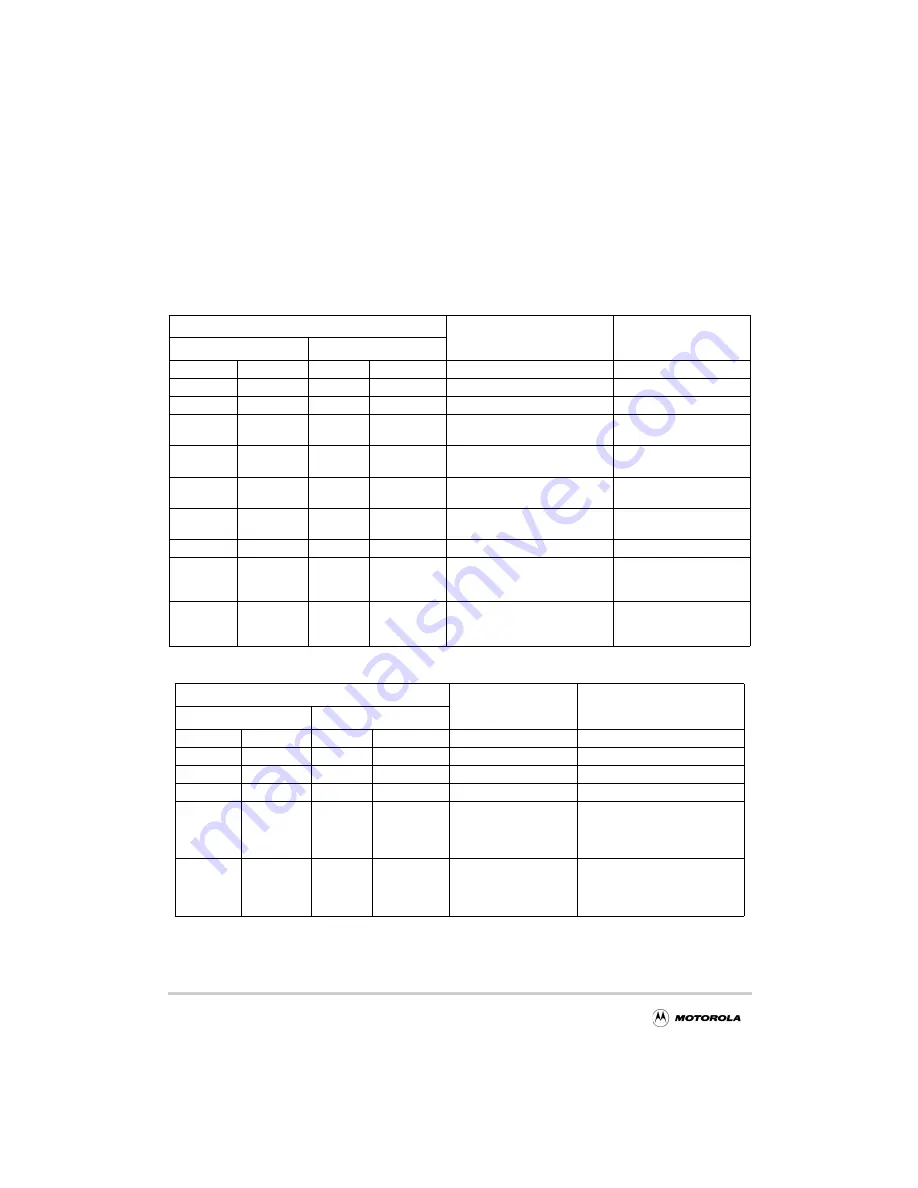

Table 3-1. Address Map B—Processor View in Host Mode

Processor Core Address Range

PCI Address Range

Definition

Hex

Decimal

0000_0000

3FFF_FFFF

0

1G - 1

No PCI cycle

Local memory space

1

4000_0000

7FFF_FFFF

1G

2G - 1

No PCI cycle

Reserved

8000_0000

FDFF_FFFF

2G

4G - 32M - 1

8000_0000–FCFF_FFFF

PCI memory space

3

FE00_0000

FE7F_FFFF

4G - 32M

4G - 32M +

64K - 1

0000_0000–0000_FFFF

PCI I/O space (8 Mbytes),

0-based

4

FE80_0000

FEBF_FFFF

4G - 24M

4G - 20M - 1

0080_0000–00BF_FFFF

PCI I/O space (4 Mbytes),

0-based

5

FEC0_0000

FEDF_FFFF

4G - 20M

4G - 18M - 1

CONFIG_ADDR

PCI configuration address

register

6

FEE0_0000

FEEF_FFFF

4G - 18M

4G - 17M - 1

CONFIG_DATA

PCI configuration data

register

7

FEF0_0000

FEFF_FFFF

4G - 17M

4G - 16M - 1

Interrupt acknowledge broadcast

PCI interrupt acknowledge

FF00_0000

FF7F_FFFF

4G - 16M

4G - 8M - 1

If ROM remote, then

FF00_0000–FF7F_FFFF; if

ROM local, then no PCI cycle

32- or 64-bit Flash/ROM

space (8 Mbytes)

8

FF80_0000

FFFF_FFFF

4G - 8M

4G - 1

If ROM remote, then

FF80_0000–FFFF_FFFF; if

ROM local, then no PCI cycle

8-, 32- or 64-bit

Flash/ROM space

(8 Mbytes)

9

Table 3-2. Address Map B—PCI Memory Master View in Host Mode

PCI Memory Transaction Address Range

Local Memory

Address Range

Definition

Hex

Decimal

0000_0000

3FFF_FFFF

0

1G - 1

0000_0000–3FFF_FFFF

Local memory space

1

4000_0000

7FFF_FFFF

1G

2G - 1

4000_0000–7FFF_FFFF

Reserved

2

8000_0000

FDFF_FFFF 2G

4G - 32M - 1

No local memory cycle

PCI memory space

10, 11

FE00_0000

FEFF_FFFF

4G - 32M

4G - 16M - 1

No local memory cycle

Reserved

11

FF00_0000

FF7F_FFFF

4G - 16M

4G - 8M - 1

If ROM local, then

FF00_0000–FF7F_FFF

F; if ROM remote, then

no local memory cycle

32- or 64-bit Flash/ROM space

(8 Mbytes). Read-only area

(writes cause Flash write error).

8

FF80_0000

FFFF_FFFF

4G - 8M

4G - 1

If ROM local, then

FF80_0000–FFFF_FFF

F; if ROM remote, then

no local memory cycle

8-, 32- or 64-bit Flash/ROM

space (8 Mbytes). Read-only

area (writes cause Flash write

error).

9

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...